* Ref(01_Adder):Уд-ие лога о результатых симуляции * Ref(01_Adder):Улучш-ие логирования * Ref(01_Adder_32):Доб-ие timeunit * Fix(01_Adder):Доб-ие #1 для ожидания line_dump * Ref(01_Adder):Доб-ие инфы в тб для 32 битного сумматора * Ref(01_Adder):Дополнение информацией board файла * Ref(01_Adder):Итализация названия рисунка 3 * Ref(01_Adder):Испр-ие грамматических ошибок в board файле * Revert "Ref(01_Adder):Доб-ие инфы в тб для 32 битного сумматора" This reverts commit96380b56dc. * Revert "Fix(01_Adder):Доб-ие #1 для ожидания line_dump" This reverts commit34670f21f8. * Revert "Ref(01_Adder_32):Доб-ие timeunit" This reverts commit11c97ac431. * Revert "Ref(01_Adder):Улучш-ие логирования" This reverts commit92147fa303. * Revert "Ref(01_Adder):Уд-ие лога о результатых симуляции" This reverts commit33c8dda06c. * Ref(01_Adder):Испр-ие грамматики в README board files * Ref(01_Adder): Применение правок по MD bordfiles после ревью Co-authored-by: Andrei Solodovnikov <VoultBoy@yandex.ru> * Ref(01_Adder):Замена рисунка в MD board_files * Ref(01_Adder):Замена текста на ссылку по прошивке плис в board_files * Style(01_Adder):Испр-ие названия рисунков * Ref(01_Adder):Доб-ие ссылки на source window в board files * Ref(01_Adder):Испр-ие орфографии в md board_files * Style(01_adder_board):Разбивка длинных строк в md * Ref(01_Adder_board_md):Доб-ие номеров в кругах * Style(01_Adder_board_md):Доб-ие диапазонов в блок кода * Ref(01_Adder_board):Переименование файлов рисунков * Ref(01_Adder_board_md):Замена html color на latex Тк mardown не поддерживает html цвета * Revert "Ref(01_Adder_board_md):Замена html color на latex" This reverts commit90762590f7. * Fix(01_Adder):Применение правок из ревью к md board files Co-authored-by: Andrei Solodovnikov <VoultBoy@yandex.ru> * Ref(01_Adder):Уд-ие лишней ссылки на инструкцию прошивки * Ref(01_Adder):Изм-ие номера рисунка * Ref(01_Adder):Переделка рисунка с 48 + 18 * Ref(01_Adder):Улучшение читаемости структурной схемы * Repo((.pic/labs/board files):Уд-ие неиспользуемых пикч * Repo(board_files):Возврат program_device * Repo:Перемещение пикчи how_to_program в соотв папку --------- Co-authored-by: Andrei Solodovnikov <VoultBoy@yandex.ru>

3.8 KiB

Как прошить ПЛИС

После того как вы описали и верифицировали модуль, остается запрототипировать его в ПЛИС. Для этого в большинстве папок лабораторных работ есть подпапка board_files в которой хранятся необходимые для этого файлы. Обычно там будет находиться модуль верхнего уровня и файл ограничений, которые позволяют связать вашу логику с периферией, расположенной на плате Nexys-A7.

Для сборки итогового проекта вам необходимо:

- Добавить модуль верхнего уровня (содержащийся в файле с расширением

.sv) вDesign Sourcesвашего проекта. - Выберете добавленный модуль в качестве модуля верхнего уровня вашего проекта.

- Для этого нажмите по нему правой кнопкой мыши.

- В контекстном меню выберете

Set as Top.

- Добавьте файл ограничений (с расширением

.xdc) вConstraintsвашего проекта. Если такой файл уже есть в вашем проекте (а он будет в нем уже после первой лабораторной), вам необходимо заменить старого файла содержимым нового. Ограничения меняются от лабы к лабе.

После выполнения указанных шагов, ваш проект готов к генерации битстрима — двоичного файла, с помощью которого реконфигурируется ПЛИС.

Для генерации битстрима вам необходимо нажать на Generate Bitstream во вкладке PROGRAM AND DEBUG окна Flow Navigator (левый нижний угол окна программы).

Рисунок 1. Расположение кнопки Generate Bitstream.

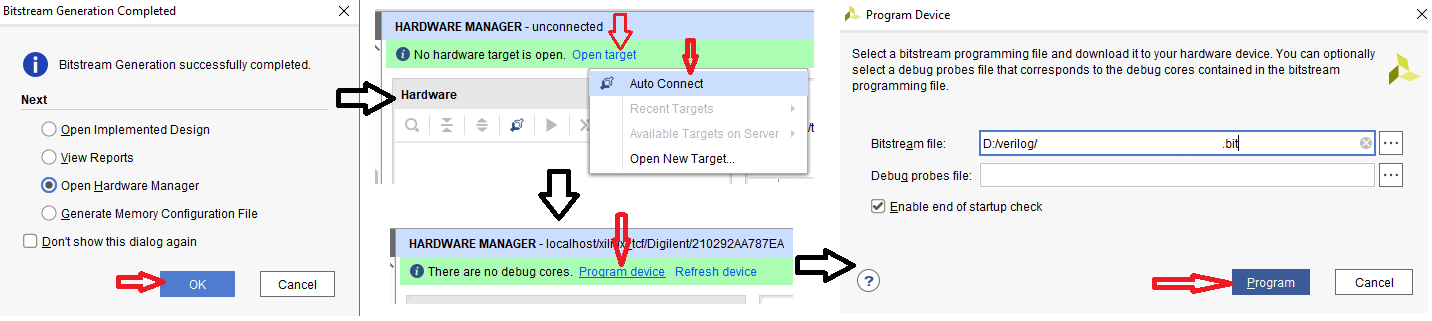

После нажатия на эту кнопку, нажимайте утвердительно во всех всплывающих окнах (варианты YES/OK, в зависимости от состояния вашего проекта, число появляющихся окон будет различным). После успешной генерации битстрима откроется окно Bitstream Generation Completed.

Остается прошить ПЛИС. Для этого подключите отладочный стенд к USB-порту компьютера и включите на стенде питание. Затем откройте окно HARDWARE MANAGER для этого:

- Убедитесь, что выбран пункт

Open Hardware Managerв окнеBitstreamи нажмите на OK. - Кликните

Open target→Auto Connect→Program device→Program.

Рисунок 2. Последовательность действий для прошивки ПЛИС.

После этого появится окно с индикатором реконфигурации ПЛИС. Когда окно закроется, в ПЛИС окажется прототип вашего модуля.