Проверка работы полного 32-битного сумматора в ПЛИС

После того, как вы создали проверили на моделировании 32-разрядный сумматор, вам необходимо проверить его работу на прототипе в ПЛИС.

Для этого вам потребуется модуль верхнего уровня nexys_adder.sv,

который позволяет связать вашу логику с периферией, расположенной на плате Nexys-A7.

Для его подключения, скачайте и добавьте файл в проект, либо скопируйте содержимое в новый

.sv файл вашего проекта. В окне Sources нажмите на него ПКМ и выберите Set as Top,

после чего в иерархии он станет главным (название главного модуля выделено жирным шрифтом).

Более подробно работа с иерархией модулей в САПР Vivado описана

здесь.

Для того, чтобы входы и выходы этого модуля были соединены с нужными входами и выходами ПЛИС,

нужно в проекте выбрать Add or create constraints и подключить файл

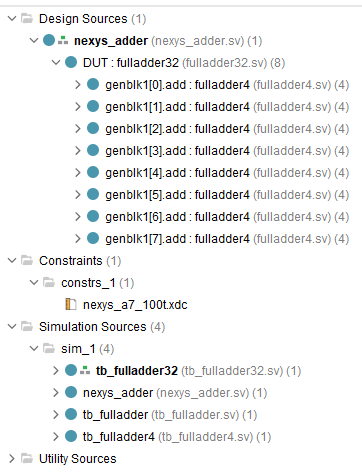

nexys_a7_100t.xdc. На рис. 1 представлен пример иерархии проекта,

готовой к созданию битстрима (двоичного файла, предназначенного для конфигурации ПЛИС таким образом,

чтобы она воспроизводила логику описанного вами модуля).

Рисунок 1. Пример иерархии проекта с модулем верхнего уровня nexys_adder.

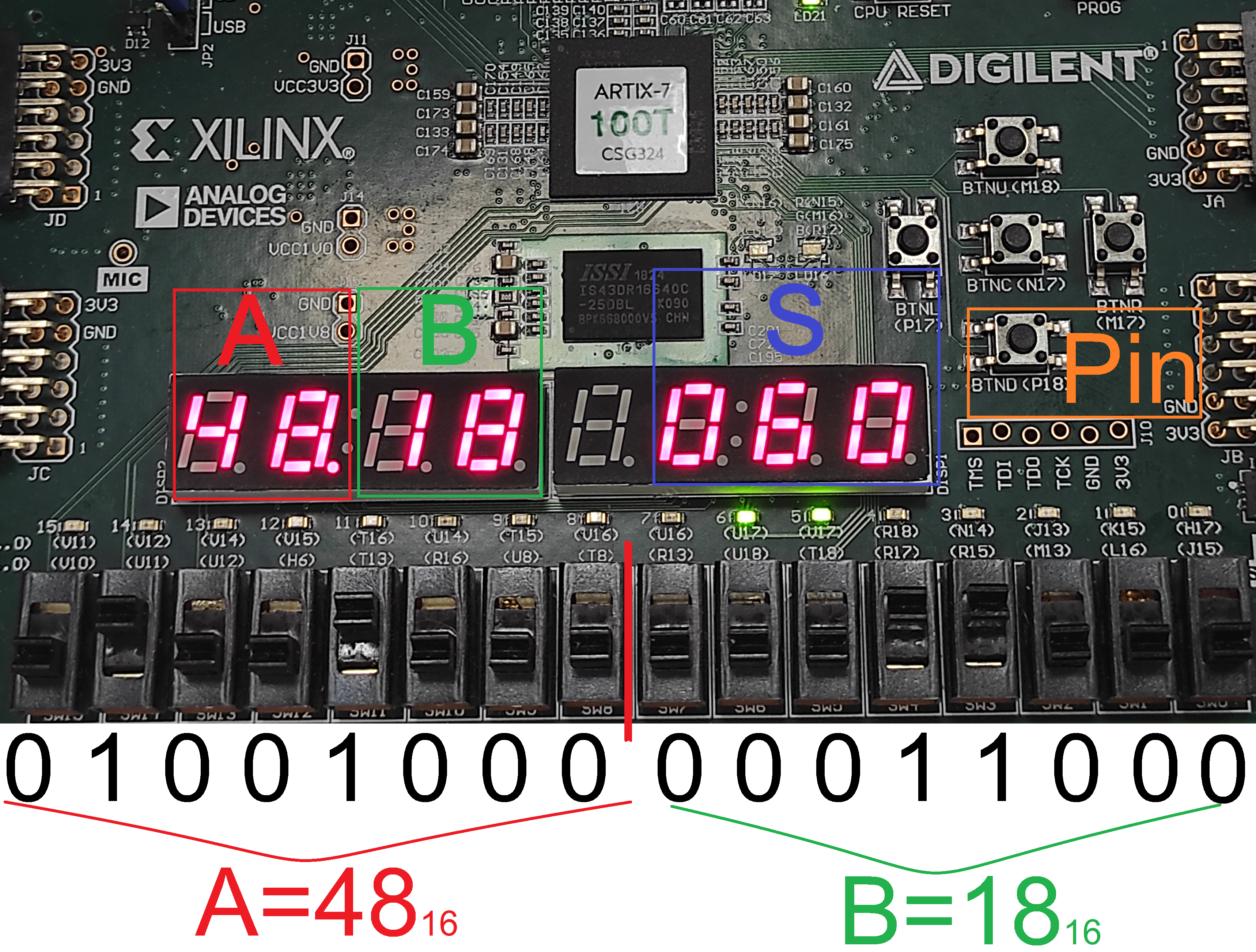

После этого наше устройство будет выглядеть, как представлено на рис. 2:

Рисунок 2. Структурная схема модуля nexys_adder.

Модуль nexys_adder позволяет подавать данные с переключателей ❶ на входы a_i, b_i,

а так же передавать входной бит переноса с помощью кнопки ❷ BTND на вход carry_i.

Переключатели делятся пополам между операндами a_i, b_i (переключатели sw[7:0] относятся к

операнду b_i, переключатели sw[15:8] относятся к операнду a_i). Так как переключателей

всего 16, каждому операнду достается только по 8. Таким образом, с переключателей можно ввести

8 младших бит каждого из операнда.

Старшие биты дополняются нулями, это значит что на нашем прототипе можно складывать числа в

диапазоне [0:255] (плюс можно прибавлять входной бит переноса),

а значит диапазон результатов будет [0:511].

Семисегментные индикаторы ❸ отображают на левом блоке значение операндов a_i и b_i

в шестнадцатеричном формате, а на правом — результат сложения. Светодиоды ❹,

расположенные над переключателями, дублируют сумму, представляя ее в двоичном формате.

На рис. 3 показано сложение (A=0x48) + (B=0x18) == 0x60 при нулевом входном переносе

(нулевом, т.к. не нажата кнопка BTND aka сигнал Pin)

Рисунок 3. Использование сумматора для вычисления выражения 0x48 + 0x18 в ПЛИС.

Дальше нужно создать битстрим и прошить его в ПЛИС по инструкции.