* Update 06. RISC-V architecture.md * Update 02. Instruments.md * Update 03. Digital arithmetics.md * Update 04. Operations units.md * Update 05. Sequencial logic.md * Update 07. RISC-V programming.md * Update 08. Singlecycle processor.md * Update 09. Multicycle processor.md * Update 10. Pipeline processor.md * Update 11. Pipeline hazards.md * Update Lectures/02. Instruments.md * Update Lectures/04. Operations units.md --------- Co-authored-by: Andrei Solodovnikov <VoultBoy@yandex.ru>

11 KiB

Лекция 6. Архитектура RISC-V

Система команд процессора — это все команды, выполнение которых аппаратно поддерживается процессором. Архитектура системы команд (Instruction Set Architecture, ISA) включает в себя систему команд и средства для их выполнения, такие как форматы данных, системы регистров, способы адресации, модели памяти. Лекция была посвящена обзору ISA RISC-V и её особенностей.

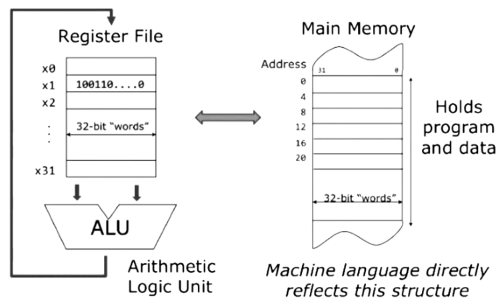

RISC (Reduced Instruction Set Computer) — архитектура с сокращённым набором команд. В таких архитектурах поддерживается относительно небольшой набор простых инструкций (обычно до 100), притом все они имеют одинаковый размер. RISC также является load/store архитектурой, это значит, что для того, чтобы выполнить какую-либо операцию над данными, их необходимо предварительно разместить в регистровом файле. Все операции происходят только с данными в регистровом файле, а для доступа к основной памяти используются специальные инструкции типа load и store.

RISC-V является RISC-архитектурой (мы рассматриваем исключительно её 32-битный вариант). Регистровый файл включает 32 регистра общего назначения, кроме регистра по адресу 0, там находится константное значение 0 (записать в него ничего не получится). Все регистры 32-битные. АЛУ выполняет операции только над данными размещёнными в регистровом файле. Основная память имеет побайтовую адресацию, при этом считывать из памяти можно байты, полуслова (16 бит) и слова (32 бита).

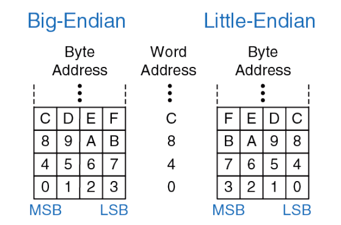

Побайтовая адресация с выровненным доступом подразумевает, что каждый байт памяти имеет свой уникальный адрес, при этом можно считать или записать также полуслово или слово, в таком случае должен быть указан адрес младшего байта, входящего в состав этого полуслова или слова. Существуют два способа организации порядка следования байт: Big-Endian и Little-Endian, при этом внутри отдельного байта число хранится обычным образом — слева старший бит, справа — младший.

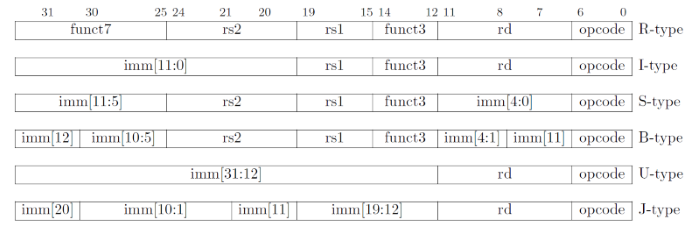

Каждая инструкция кодируется 32 битами. Чтобы не использовать инструкции представленные в машинном коде (нулями и единицами), их записывают с помощью инструкций языка ассемблера. Язык ассемблера представляет собой машинные коды, записанные в виде понятной человеку мнемоники. Например, машинная инструкция 00000000001100010111000010000011 для RISC-V записывается на языке ассемблера как and x1, x2, x3 — это понятней и наглядней, чем машинная инструкция. Разные архитектуры процессоров имеют разные ассемблеры.

Типичная команда ассемблера начинается с короткого слова, указывающего что нужно сделать, далее указывается с какими данными это надо сделать. Названия регистров состоят из буквы x и номера регистра, например, x10 — это десятый регистр регистрового файла.

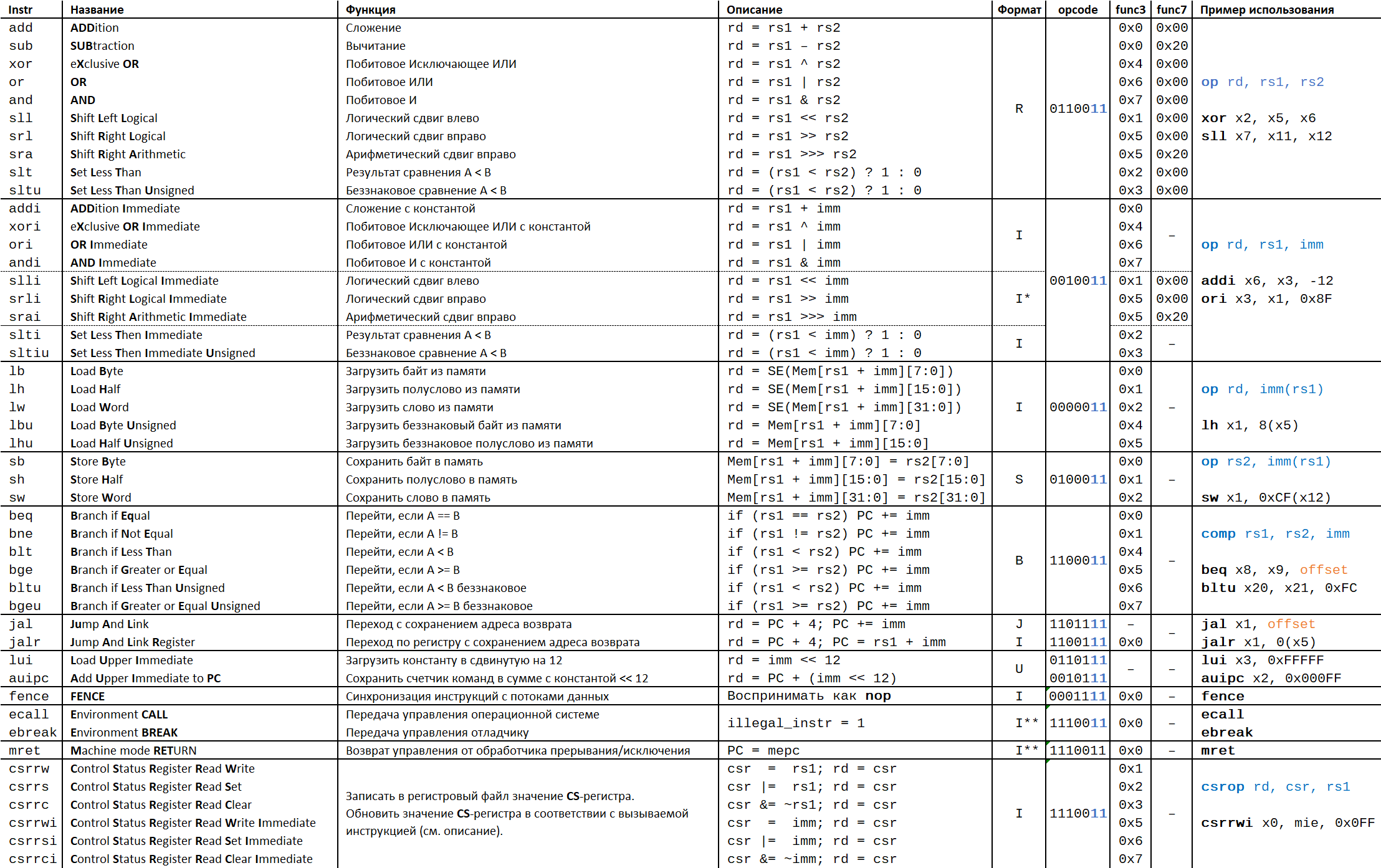

Базовый набор целочисленных инструкций архитектуры RISC-V включает в себя:

-

10 вычислительных инструкций, использующих в качестве двух операндов значения из регистров, и помещающее результат в регистровый файл

add x4, x3, x2 # сложение x4 = x3 + x2 or x8, x5, x1 # логическое ИЛИ x8 = x5 | x1 sll x5, x4, x3 # логический сдвиг влево x5 = x4 << x3 # и тому подобное -

9 вычислительных инструкций, использующих в качестве одного из операндов регистр из регистрового файла, а второго — константу из инструкции

addi x4, x3, -5 # сложение x4 = x3 + (-5) srli x5, x4, 2 # логический сдвиг вправо x5 = x4 >> 2 # и тому подобное -

8 инструкций для перемещения данных между регистровым файлом и основной памятью, использующих косвенно-регистровую адресацию со смещением (это значит, что адрес ячейки в основной памяти вычисляется как сумма базового регистра и смещения)

lw x4, 8(x7) # загрузить слово (32 бита) из памяти # по адресу x7 + 8 в регистр x4 lbu x3, 0(x2) # загрузить беззнаково байт (8 бит) из памяти # по адресу x2 + 0 в регистр x3 sw x2, 16(x5) # переместить данные из регистра x2 в память по адресу x5 + 16 -

6 инструкций условного перехода, сравнивающих значение из двух регистров

beq x14, x15, label # если x14 == x15, то PC = PC + label blt x20, x21, label # если x20 < x21, то PC = PC + label # label - это метка, представляющая собой обычное число -

2 инструкции безусловного перехода с сохранением адреса возврата

jal x3, label # x3 = PC + 4; PC = PC + labelИ ещё несколько специфических инструкций. Полный список базовых целочисленных инструкций форматы их кодирования приводятся ниже.

Кроме озвученных инструкций существуют и псевдоинструкции - псевдонимы существующих инструкций для упрощенного программирования на ассемблере. Например, инструкция

mv x2, x1 # переместить данные из регистра x1 в x2

на самом деле является инструкцией

addi x2, x1, 0

Основные материалы лекции

- Ссылка на видеозапись лекции

- Все материалы лекции можно найти в этом источнике, к сожалению аналога на русском пока не нашел [Patterson Hennessy. Computer organization and design. RISC-V edition — 2 глава]

Дополнительные материалы к лекции для саморазвития

- Понятный разбор очень похожей архитектуры MIPS [Харрис и Харрис. Цифровая схемотехника и архитектура компьютера — параграфы 6.1, 6.2]

- Еще один годный разбор другой популярной RISC архитекрутры — ARM [Харрис и Харрис. Цифровая схемотехника и архитектура компьютера. Дополнение по архитектуре ARM — параграфы 1.1, 1.2]

- Обзор популярной тройки: x86, ARM, AVR [Таненбаум и Остин. Архитектура компьютера — Глава 5]

Популярные материалы

- На этом сайте можно сразу писать код на языке ассемблера RISC-V, запускать, отлаживать, а потом еще и машинный код сохранить себе

- Расширение для VSCode ассемблера и дебаггера RISC-V

- Немного мёда про RISC-V

- Отличнейшая популярная книга о цифровой схемотехнике и архитектуре компьютера, рекомендую заглянуть в нее при любом уровне понимания материала. Объем не большой, страницы маленькие, буквы большие, за пару полных вечеров вполне читается, многое проясняет и ставит на место [Чарльз Петцольд. Код. Тайный язык информатики]