mirror of

https://github.com/MPSU/APS.git

synced 2025-09-15 17:20:10 +00:00

2.7 KiB

2.7 KiB

Лабораторная работа 11 "Интеграция подсистемы прерываний"

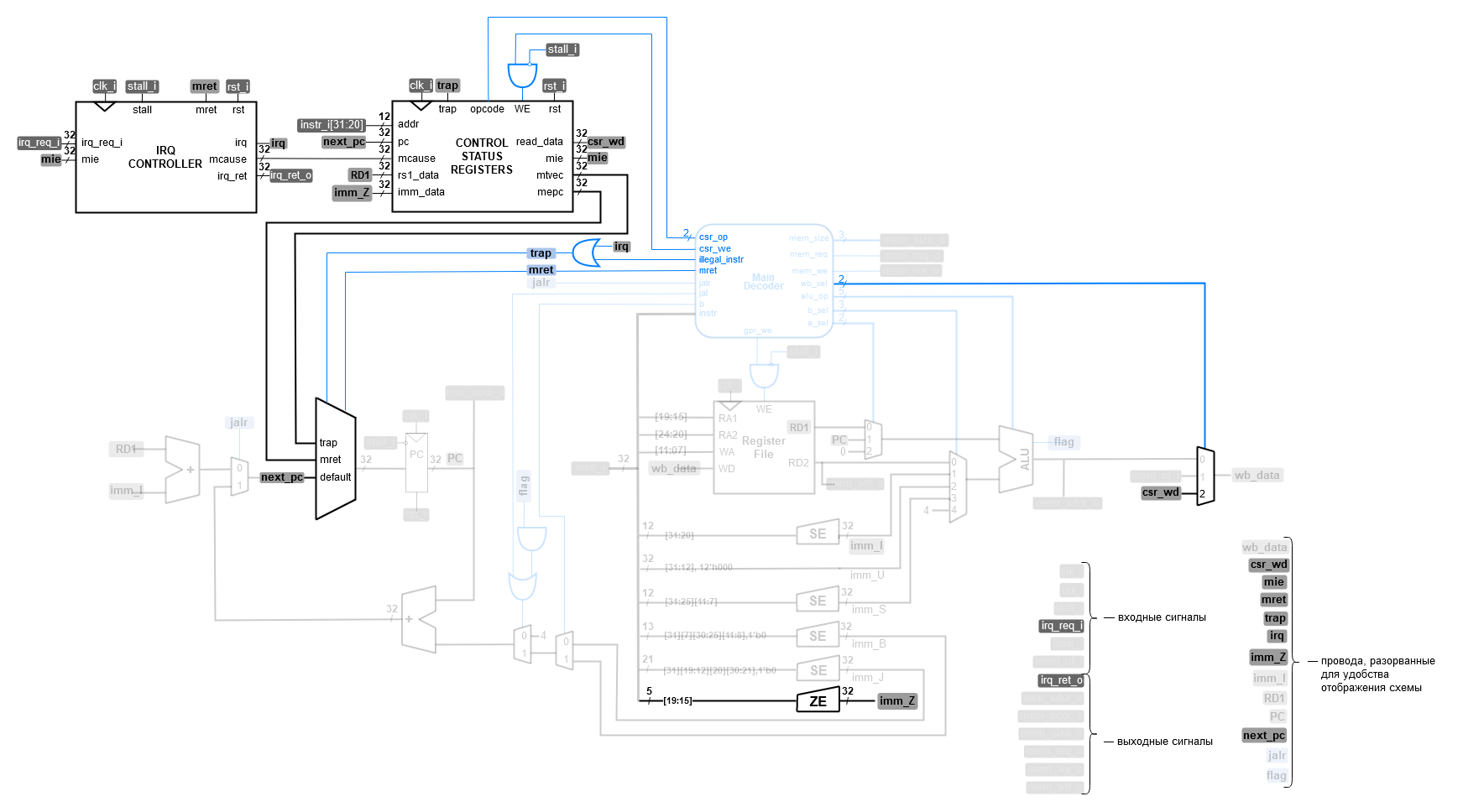

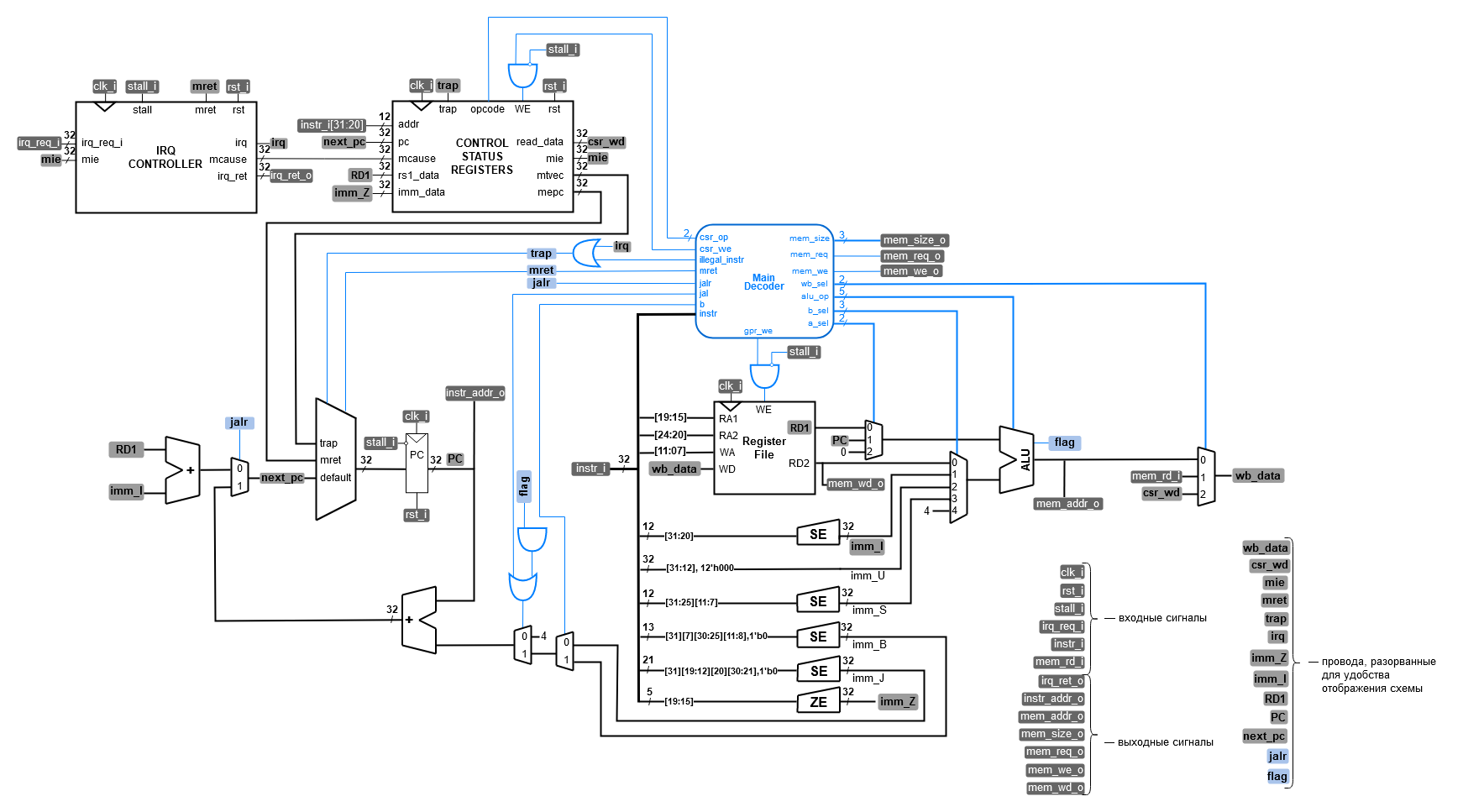

После реализации подсистемы прерываний, её необходимо интегрировать в процессорную систему. Для этого необходимо обновить модуль riscv_core по приведенной ниже схеме:

Задание

Интегрировать модули csr_controller и irq_controller в модуль riscv_core.

Порядок выполнения работы

-

Интегрируйте модули

csr_controllerиirq_controllerв модульriscv_core.- Обратите внимание, что что в модуле

riscv_coreпоявились новые входные и выходные сигналы. Эти сигналы должны быть подключены и в модулеriscv_unit(просто в виде проводов, которые с другой стороны не подключены ни к чему, в следующей лабораторной мы найдем им применение). - Большой мультиплексор на схеме, определяющий записываемое в

PCзначение является мультиплексором с приоритетами (в первую очередь проверяется сигналtrap, затем, если он равен нулю, проверяется сигналmret, и только если оба предыдущих равны нулю выдается значениеdefault). Такой мультиплексор можно описать как на цепочке выраженийif-else-if, так и с помощью выраженияcaseв качестве управляющего сигнала которого подана единица, а выбор осуществляется не по значениям, а по сигналам:

case(1'b1) a: ... b: ... c: ... - Обратите внимание, что что в модуле

-

После интеграции модулей, проверьте процессорную систему с помощью программы из ЛР10 с помощью предоставленного тестбенча.