21 KiB

Лекция 15. Память

Содержание

- Лекция 15. Память

Определение

Система памяти — это функциональный блок микропроцессорной системы, предназначенный для временного или постоянного хранения данных и команд, состоящий из запоминающего устройства и устройства управления.

Характеристики

- Ёмкость — это количество битов данных, которые запоминающее устройство может хранить единовременно.

- Единица пересылки — это количество битов данных, передаваемых по линиям шины одновременно.

- Быстродействие состоит из нескольких характеристик:

- Время выборки данных — это время между началом формирования запроса к памяти и получения первых бит информации на выходах из памяти.

- Время хранения данных

- Период обращения — это минимальное время, которое должно пройти между обращениями к памяти.

- Скорость передачи данных

P.S. Стоит отметить, что не существует памяти, которая будет одновременно и ёмкой, и быстрой, и дешёвой в производстве. В любом случаем придётся жертвовать одним из трёх пунктов.

Метод доступа к данным

- Произвольный — метод, который просто возвращает данные по указанному адресу (RAM — Randoom Access Memory).

- Последовательный — метод, при котором перед получением данных нужно прочитать все ячейки памяти, находящиеся до нужного адреса (видеокассета).

- Прямой — это метод при котором поиск макроячейки осуществляется произвольным методом, а внутри макроячейки осуществляется последовательный поиск нужной ячейки.

- Ассоциативный — это метод, при котором поиск осуществляется по тегам (Кэш-память).

Иерархия памяти

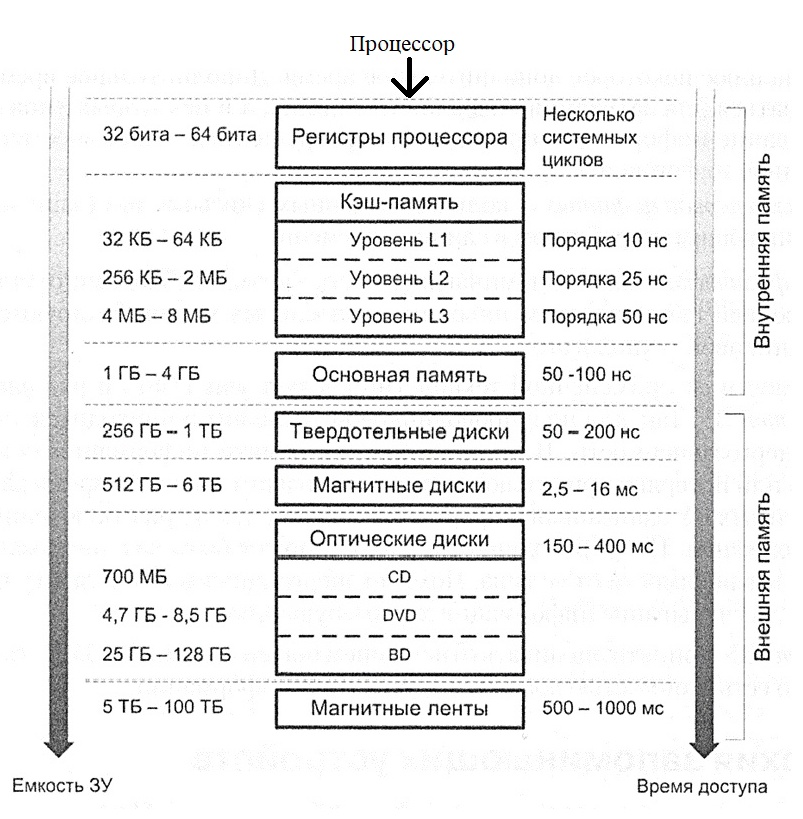

С течением времени производительность процессора увеличивалась в разы быстрее чем производительность памяти, вследствие чего память отделилась от процессора и стала отдельным блоком. Из-за этого появилась иерархия памяти (см. рис. 1). Память в компьютере состоит из нескольких уровней, которые условно разделены на две части: внутренняя и внешняя. Внутренняя нужна для функционирования системы, а внешняя для хранения больших данных, которые могут быть использованы процессором не так часто.

Рис. 1. Иерархия памяти.

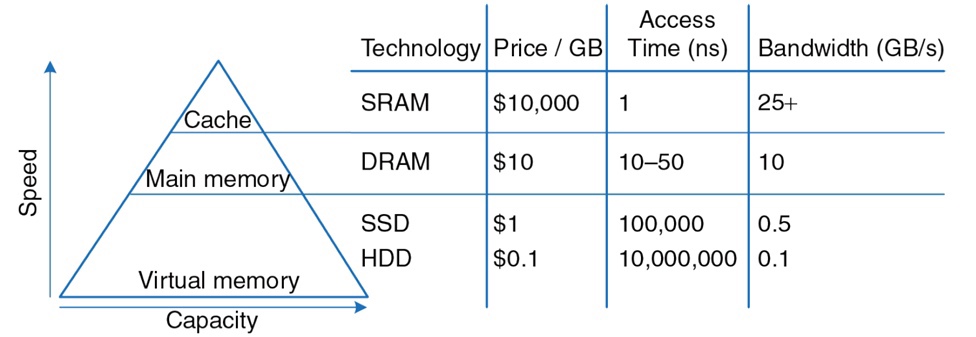

В иерархии памяти можно выделить несколько зависимостей (см. рис. 2):

- Чем ближе часть памяти к процессору, тем меньше у неё ёмкость и тем она быстрее работает.

- Чем ближе часть памяти к процессору, тем чаще тот к ней обращается.

- Чем дальше от процессора, тем дешевле единица памяти. Т.е. гигабайт магнитной ленты стоит во много раз дешевле гигабайта кэш-памяти.

Рис. 2. Зависимости в иерархии памяти.

Локальность по обращению

Обращения к памяти обладают временной и пространственной локальностью:

Временная локальность — это понятие, отражающее закономерность обращений программ к памяти и, с высокой вероятностью, проявляющееся в повторном использовании данных, к которым недавно уже обращались.

Пространственная локальность — это понятие, отражающее закономерность обращений программ к памяти и, с высокой вероятностью, проявляющееся в использовании в ближайшем будущем данных, находящихся по соседним адресам.

Именно из-за этих понятий 90% времени работы программы связано с доступом к 10% адресного пространства этой программы. Если 10% адресного пространства поместить на быстродействующую память (Например кэш-паять), то 90% времени процессор будет работать с памятью на высокой скорости. Поэтому и существует иерархия памяти, которая помогает обходить проблему с быстротой, ёмкостью и дешевизной отдельных уровней памяти. Т.е. если взять быструю, маленькую и дешёвую кэш-память и медленную, большую и дешёвую оперативную память, то получится иерархия памяти, обладающая быстротой, ёмкостью и дешевизной. Это и есть главная причина возникновения иерархии.

Статическая и динамическая память

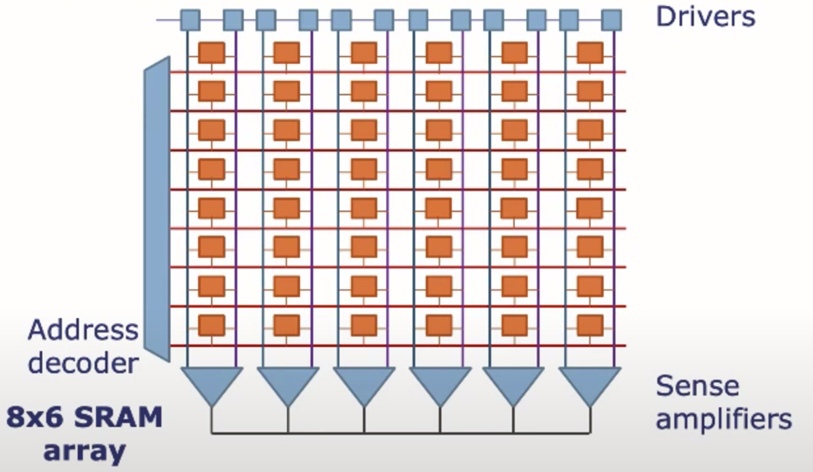

Статическая память (SRAM) — это память, сделанная из транзисторов (см. рис. 3). Адрес ячейки подаётся на address decoder, с помощью которого определяется с какой ячейки считывать/записывать данные. На drivers подаются данные, которые будут использованы для записи. На выходе стоят усилители сигнала — Sense amplifiers. Обычно из статической памяти делается кэш-память.

Рис. 3. Статическая память.

Рассмотрим теперь отдельную ячейку памяти (см. рис. 4). Ячейка статической памяти состоит из двух инверторов, которые в свою очередь состоят из двух транзисторов (Например М1 и М2). Эти два инвертора подключены так, что выход первого соединён со входом второго, а выход второго со входом первого. Таким образом, они образуют бистабильную ячейку. Также существуют транзисторы M5 и M6, которые являются ключами, позволяющие положить в эту ячейку либо 0, либо 1. Итого для организации одной статической ячейки памяти требуется 6 транзисторов.

Рис. 4. Ячейка статической памяти.

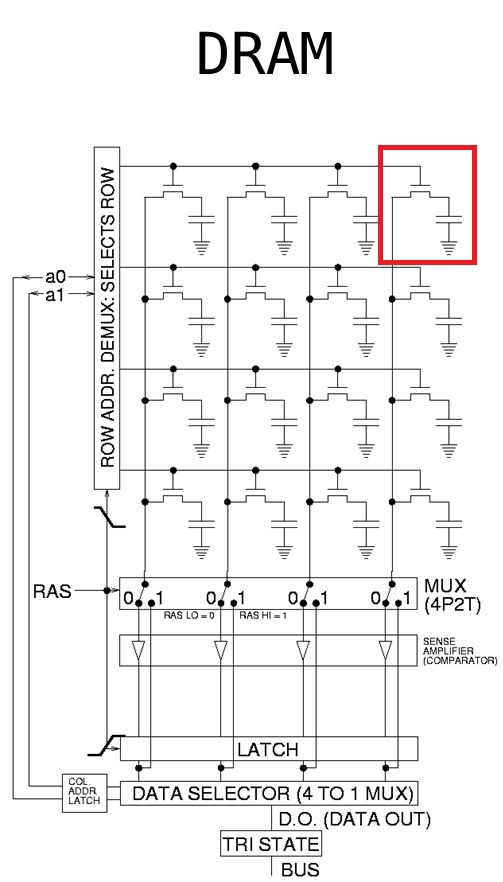

Динамическая память (DRAM) — это память, состоящая из конденсаторов (см. рис. 5). Обычно из статической памяти делается оперативная память.

Ячейка динамической памяти (красный прямоугольник) состоит из одного конденсатора и одного транзистора, являющегося ключом. Если конденсатор заряжен, то в ячейке хранится 1, если разряжен — 0.

Рис. 5. Динамическая память.

Регенерация DRAM

Ввиду малых размеров конденсатора (а значит и его ёмкости), записанная на нем информация хранится крайне недолго — буквально сотые, а то тысячные доли секунды. Причина тому — саморазряд конденсатора. Для борьбы с "забывчивостью" памяти прибегают к ее регенерации — периодическому считыванию ячеек с последующей перезаписью. Во время регенерации все процессы, связанные с работой с памятью, останавливаются.

Сравнение SRAM и DRAM

| Критерий | SRAM | DRAM |

|---|---|---|

| Доступ к ячейки памяти | В любой момент времени | Недоступна во время регенерации |

| Кол-во элементов для одной ячейки памяти | 6-8 элементов | 2 элемента |

| Стоимость кб памяти | Высокая стоимость | Низкая стоимость |

| Стабильность | Произвольное содержимое памяти после включения | Данные обнуляются после выключения |

| Скорость работы | 10-50 нс. | До 100 нс. |

| Применение | Кэш-память | Оперативная память |

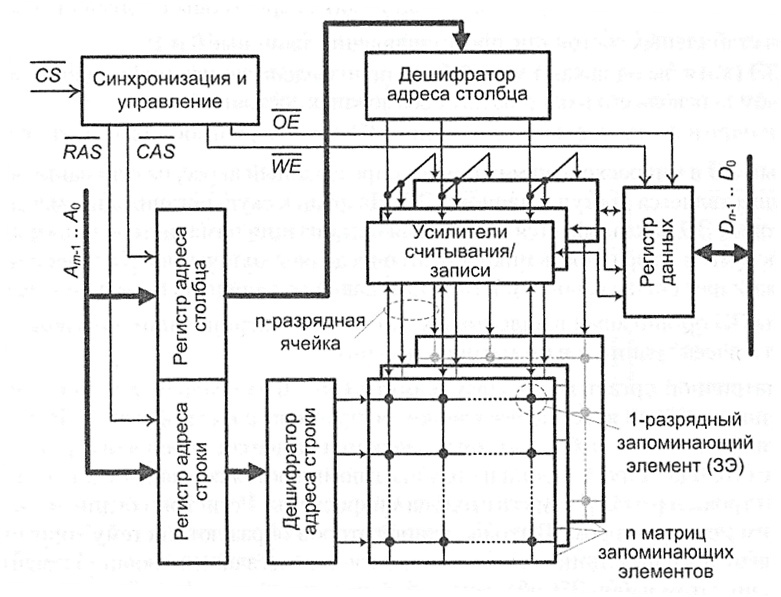

Структура микросхемы памяти

Рассмотрим структуру устройства микросхемы памяти (см. рис. 6). На вход подаётся адрес ячейки Am...A0. С помощью дешифратора адреса столбца и дешифратора адреса строки выделяется нужная ячейка памяти. С помощью усилителя считывания на выход подаётся информация с нужной ячейки памяти, которая в дальнейшем идёт на процессор. Также в схеме присутствует устройство синхронизации и управления, которое отвечает за корректную работу всех элементов схемы.

Рис. 6. Структура микросхемы памяти.

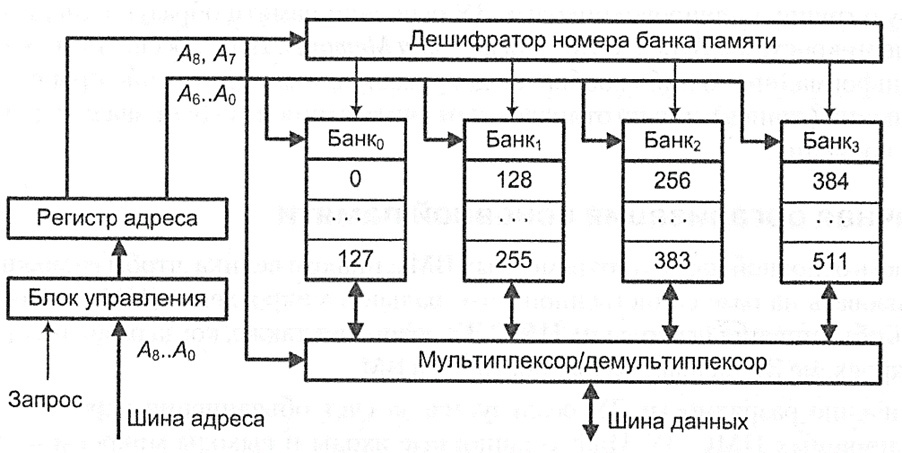

Блочная память

Иногда не удаётся сделать память единым блоком, и для увеличения адресного пространства применяется блочную память (см. рис. 7). В данной схеме банк памяти может хранить только семибитные адреса, а для получения девятибитного адресного пространства надо объединить четыре таких банка. Для управления ними используется дешифратор номера банка, которому на вход подаётся два старших бита адреса, а остальные младшие 7 бит идут сразу на все банки. В результате на шину данных придёт информация из нужной ячейки.

Рис. 7. Блочная память.

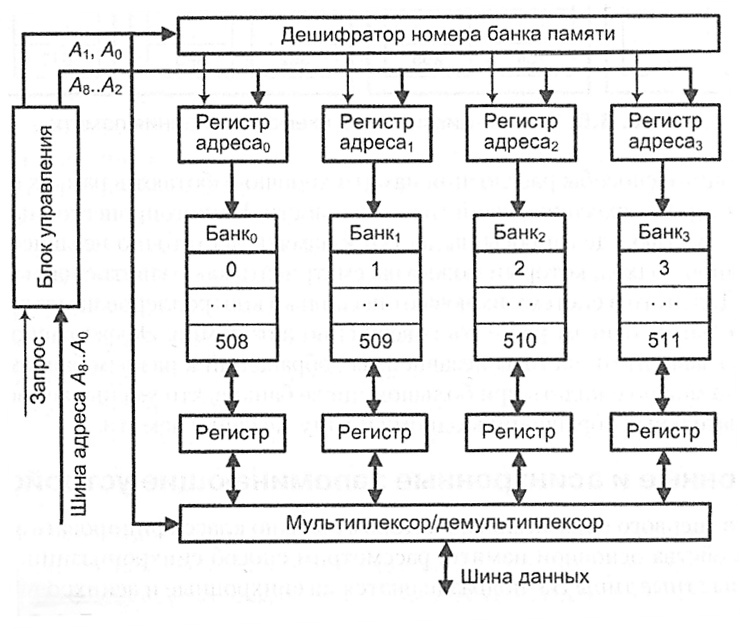

Расслоение памяти

У схемы блочной памяти, рассмотренной в прошлом примере, есть недостаток: если обращения идут к соседним ячейкам памяти, что происходит довольно часто из-за пространственной локальности, то обработка этих обращений будет осуществляться тоже последовательно. Эта проблема решается использованием расслоения памяти (см. рис. 8), т.е. соседние адреса будут находиться в разных банках памяти, вследствие чего запросы к соседним ячейкам памяти будут обрабатываться параллельно.

Рис. 8. Расслоение память.

Способы доставки данных

- Последовательный режим (flow through mode)

- Регистровый (register to latch)

- Быстрый постраничный (fast page mode)

- Пакетный (burst mode)

- Конвейерный (pipelined mode)

- Метод удвоенной скорости (double data rate)

Стоит отметить, что все современные компьютеры используют метод удвоенной скорости.

Энергонезависимая память

- Энергонезависимая память сохраняет свое состояние даже при отключении питания

- ROM: программируется на этапе производства

- Программируемая ROM (PROM): может быть запрограммирована пользователем один раз

- Стираемая PROM (EPROM): может быть стерта (УФ, рентген)

- Электрически стираемая PROM (EEPROM): стирание происходит через подачу электрического сигнала

- Flash-память: EEPROM с частичной возможностью стирания (по секторам)

- Сфера применения энергонезависимой памяти

- Встраиваемые программы размещаются в ROM (BIOS, контроллеры дисков, сетевых и графических адаптеров, аппаратно-криптографические средства,…)

- Твердотельные накопители (SSD)

- Кеш в обычных дисковых накопителях

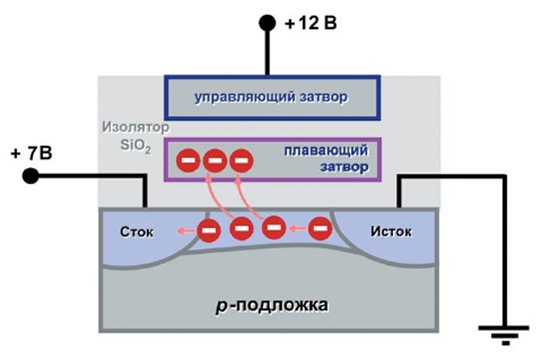

Flash-память

Рассмотрим устройство ячейки flash-памяти (см. рис. 9). Она очень похожа на транзистор, за исключением наличия плавающего затвора, который находится внутри изолятора. Если подать большое напряжение на вход, то некоторые электроны "перепрыгнут" на плавающий затвор. Чем больше напряжение подаём, тем больше электронов будет перепрыгивать на этот затвор. С помощью этого можно задать, несколько уровней заряженности плавающего затвора, тем самым уже можно закодировать несколько бит информации (Например для 2 битов информации потребуется 4 уровня заряженности). Есть один минус у этого: чем больше уровней, тем ниже надёжность этой памяти.

Рис. 9. Flash-память.

Защита памяти

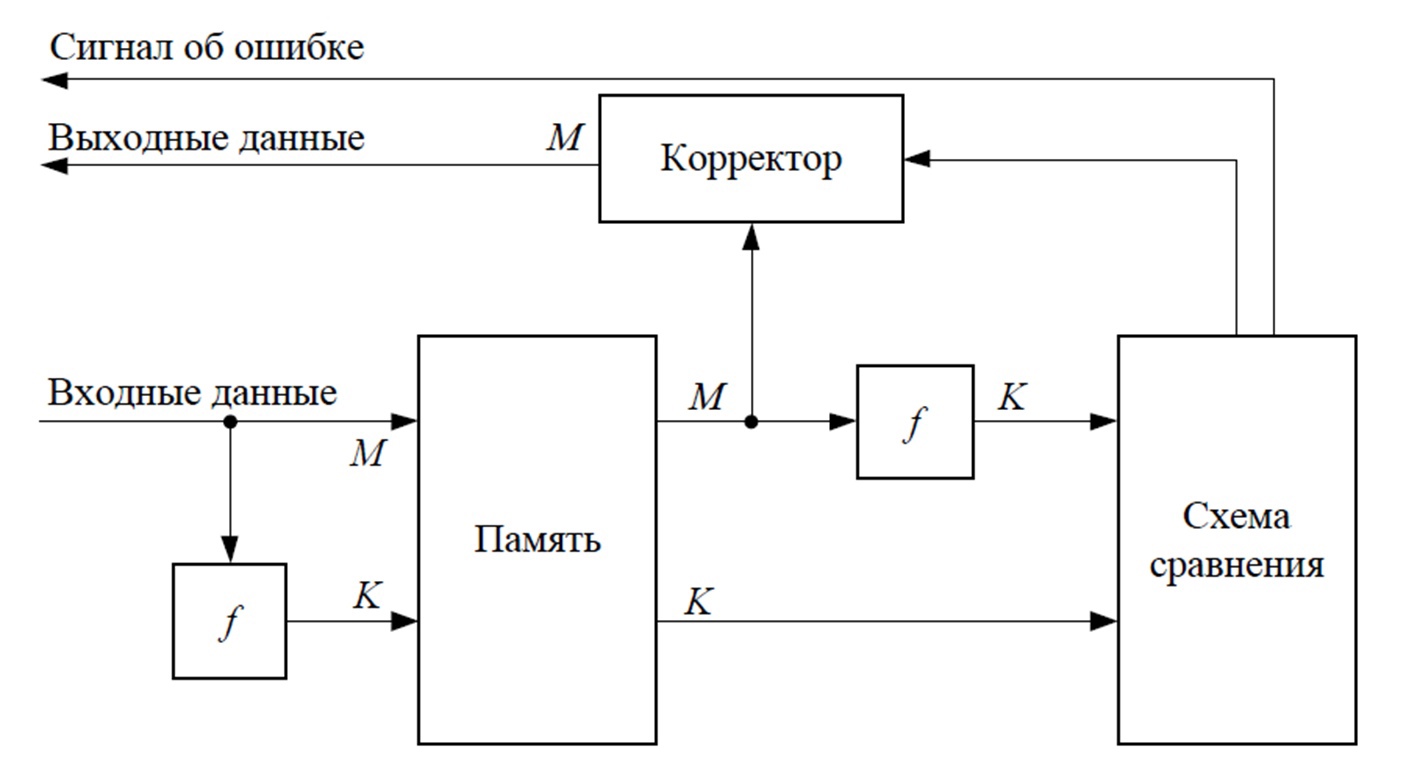

Некоторые системы требуют повышенную надёжность для памяти (например, система бортового управления самолёта). Рассмотрим пример подобной схемы (см. рис. 10). На вход подаётся M бит входных данных. Они записываются в память и (одновременно с этим) преобразуются с помощью блока F (например, хэшируется) в K бит, которые тоже записывается в эту память. Когда исходная информация возвращается из памяти, её снова преобразуют по тому же алгоритму и сравнивают с результатом исходного преобразования: если те совпадают, то информация подаётся на выход, если нет, то выдаётся сигнал об ошибке. В некоторых схемах, этих избыточных K бит данных даже достаточно, чтобы исправить некоторое количество битых бит в исходных M бит данных.

Рис. 10. Память с повышенной надёжностью.

Основные материалы лекции

- Ссылка на видеозапись лекции