* СП. Обновление предисловия * СП. Обновление введения * СП. Обновление лаб * СП. Обновление доп материалов * СП. Введение * СП. Введение * СП. ЛР№4, 15 * СП. Базовые конструкции Verilog * Update Implementation steps.md * СП. ЛР 4,5,7,8,14 * СП. ЛР№8 * Синхронизация правок * СП. Финал * Исправление ссылки на рисунок * Обновление схемы * Синхронизация правок * Добавление белого фона .drawio-изображениям * ЛР2. Исправление нумерации рисунка

6.3 KiB

О регистрах контроля и статуса

Для поддержания работы операционной системы, виртуализации, системы прерывания (но не ограничиваясь ими), в архитектуре RISC-V предусмотрено использование группы регистров, под общим названием регистры контроля и статуса (Control and Status Registers, CSR), обеспечивающих управление элементами процессора и доступ к статусной информации о системе. С помощью этих регистров реализуются привилегированные режимы работы процессора, хранение указателей на различные программные стеки, статус различных подсистем, регистры для обеспечения перехватов и многое другое.

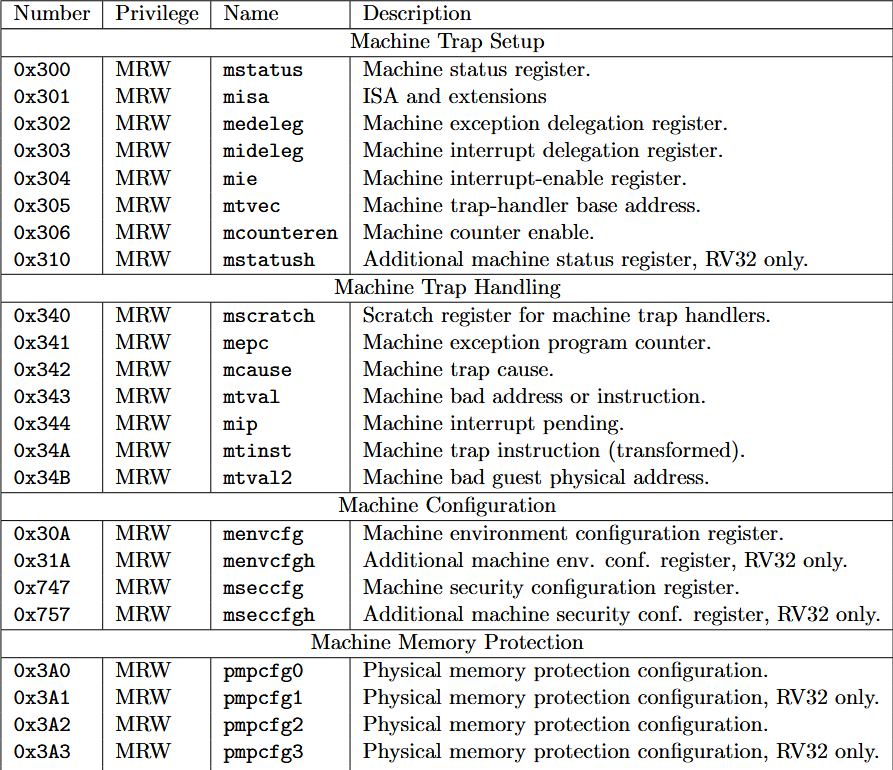

Все регистры имеют уникальные 12-битные адреса, а их роли определены в спецификации на архитектуру RISC-V. В Таблице 1 приводится фрагмент спецификации привилегированной архитектуры[1, стр. 17], иллюстрирующая некоторые из регистров. В левом столбце указан 12-битный адрес. Далее указывается в каком режиме, что можно делать с этим регистром. После идёт название, а в правом столбике описание.

В этой таблице можно увидеть регистры для сохранения адреса возврата из перехвата, адрес вектора прерывания, регистры причины (cause), регистры настройки безопасности и защиты памяти. И это далеко не полный список регистров, предоставляемых стандартом (который помимо прочего, оставляет место в адресном пространстве для ваших собственных регистров).

Таблица 1. Регистры контроля и статуса машинного (наивысшего) уровня привилегий.

Для работы с CS-регистрами используются специальные SYSTEM-инструкции I-типа (с опкодом 1110011), хранящие в 12-битном поле imm адрес регистра, к которому будет осуществлён доступ и адреса в регистровом файле откуда будет считан или куда будет записан один из CS-регистров.

| opcode | func3 | Тип | Инструкция | Описание | Операция |

|---|---|---|---|---|---|

| 1110011 | 000 | I | mret | Возврат из перехвата | PC = mepc |

| 1110011 | 001 | I | csrrw rd, csr, rs1 | Чтение и Запись CSR | rd = csr, csr = rs1 |

| 1110011 | 010 | I | csrrs rd, csr, rs1 | Чтение и Установка бит CSR | rd = csr, csr = csr | rs1 |

| 1110011 | 011 | I | csrrc rd, csr, rs1 | Чтение и Очистка бит CSR | rd = csr, csr = csr & ~rs1 |

| 1110011 | 101 | I | csrrwi rd, csr, rs1 | Чтение и Запись CSR | rd = csr, csr = imm |

| 1110011 | 110 | I | csrrsi rd, csr, rs1 | Чтение и Установка бит CSR | rd = csr, csr = csr | imm |

| 1110011 | 111 | I | csrrci rd, csr, rs1 | Чтение и Очистка бит CSR | rd = csr, csr = csr & ~imm |

Таблица 2. Список инструкций для работы с регистрами контроля и статуса.

Important

Обратите внимание на инструкции

csrrwi,csrrsi,csrrci. Эти инструкции используют 19-15 биты в качестве беззнаковой константы (несмотря на то, что согласно способу кодирования инструкций I-типа, эти биты должны интерпретироваться какrs1). Данная 5-битная константа — единственная, которая расширяется нулями.

Для удобства программирования на языке ассемблера RISC-V существуют псевдоинструкции для работы с CSR.

| Псевдоинструкция | Инструкция RISC-V | Описание | Операция |

|---|---|---|---|

| csrr rd, csr | csrrs rd, csr, x0 | Чтение CSR | rd = csr |

| csrw csr, rs1 | csrrw x0, csr, rs1 | Запись CSR | csr = rs1 |

Таблица 3. Псевдоинструкции для работы с регистрами контроля и статуса.

Операция логического ИЛИ нулевого регистра регистрового файла с содержимым регистра из блока CSR не меняет его содержимого, поэтому при использовании инструкции csrr происходит только операция чтения. Подобным образом реализована псевдоинструкция csrw.