* Update 06. RISC-V architecture.md * Update 02. Instruments.md * Update 03. Digital arithmetics.md * Update 04. Operations units.md * Update 05. Sequencial logic.md * Update 07. RISC-V programming.md * Update 08. Singlecycle processor.md * Update 09. Multicycle processor.md * Update 10. Pipeline processor.md * Update 11. Pipeline hazards.md * Update Lectures/02. Instruments.md * Update Lectures/04. Operations units.md --------- Co-authored-by: Andrei Solodovnikov <VoultBoy@yandex.ru>

11 KiB

Лекция 3. Цифровая арифметика. Арифметико-логическое устройство

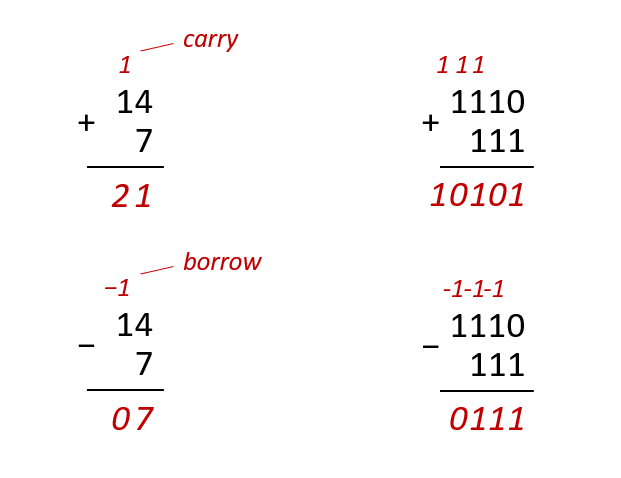

На этой лекции мы вспомнили, как складываются числа, на примере сложения в столбик. Для двоичных и десятичных чисел это делается одинаково. Разряды чисел складываются с учетом переносов от прошлых разрядов.

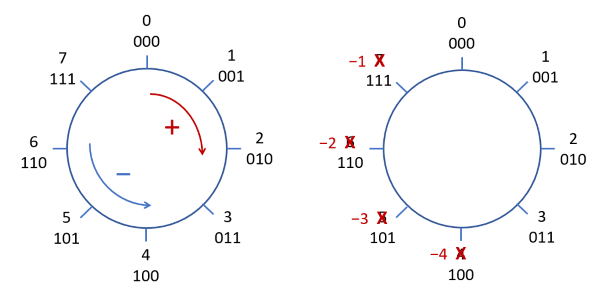

Особенностью цифровой арифметики является то, что она модульная, то есть ограничена некоторым максимальным числом, больше которого не существует. В данном случае модульная арифметика ограничена разрядностью цифрового устройства. Например, 3-битный сумматор не может выдать число, больше 111₂, то есть 7 в десятичной системе счисления. Можно сказать, что в такой арифметике не числовая прямая, а числовой круг. Операции сложения и вычитания — это движение по этому кругу в одну или в другую сторону. Благодаря особенностям такой арифметики можно выполнять вычитание используя операцию сложения. Выражение (A — B) эквивалентно выражению (A + ~B + 1). При этом к числам можно относиться либо как к беззнаковым (только положительным), либо как к знаковым (в таком случае старший бит числа указывает на знак, 1 — минус).

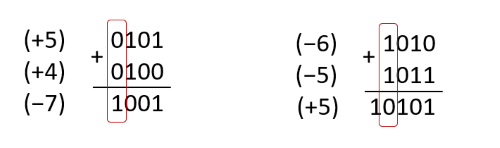

В зависимости от того используются ли числа в дополнительном коде (отрицательные) или нет по-разному определяется переполнение, то есть когда результат выходит за разрядную сетку и, следовательно, не является достоверным. Если предполагается, что операция производится только над положительными числами, то переполнением считается появление переноса от старшего разряда. Если же предполагается, что в операции используются и положительные и отрицательные числа, то переполнением является ситуация, в которой знак результата операции отличается от одинаковых знаков операндов.

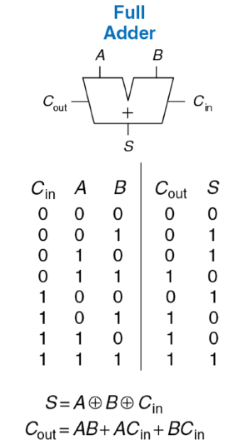

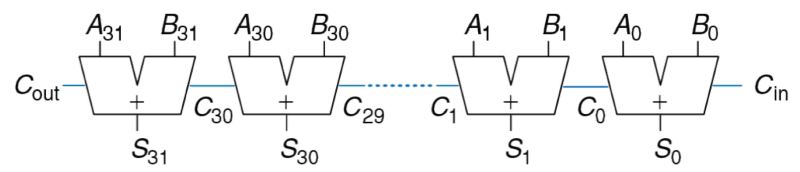

Операции сложения и вычитания выполняются на одном из основных модулей процессора — сумматоре. Он строится из нескольких простых полных однобитных сумматоров, складывающих три бита: по одному биту от каждого из операндов и входной бит переноса (от предыдущего разряда), и формирующих в качестве результата два бита: бит суммы и бит переноса для следующего разряда.

Чем больше однобитных сумматоров, тем выше разрядность обрабатываемых данных — это хорошо. Однако, в таком случае удлиняется и цепь переноса проходящая через все разряды, а значит удлиняется критический путь, то есть устройство работает медленнее — это плохо.

Если вложиться хитростью и дополнительными аппаратными затратами, то можно реализовать ускоренный перенос, уменьшающий критический путь. К таким устройствам относятся схема с ускоренным переносом и префиксный сумматор.

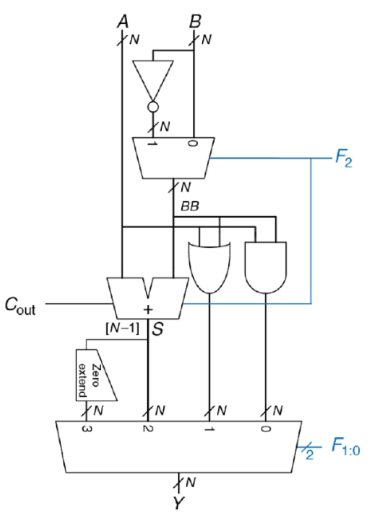

Один из основных операционных устройств (то есть устройств, выполняющих операции над данными) является АЛУ (арифметико-логическое устройство). АЛУ — это комбинационная схема выполняющая различные арифметические и поразрядно логические (то есть не использующие бит переноса) операции над входными данными. Выполняемая операция определяется управляющими сигналами. Помимо результата на выходе могут формироваться флаги, например, переполнения, знак результата и тому подобное.

Мы рассмотрели два основных подхода к проектированию. При первом подходе операции над данными мультиплексируются, и выбор операции происходит за счет управления мультиплексором.

В рассмотренном АЛУ поддерживается 7 операций (операция 011 бессмысленна). Плюс такого подхода — простота проектирования, простота изменения структуры.

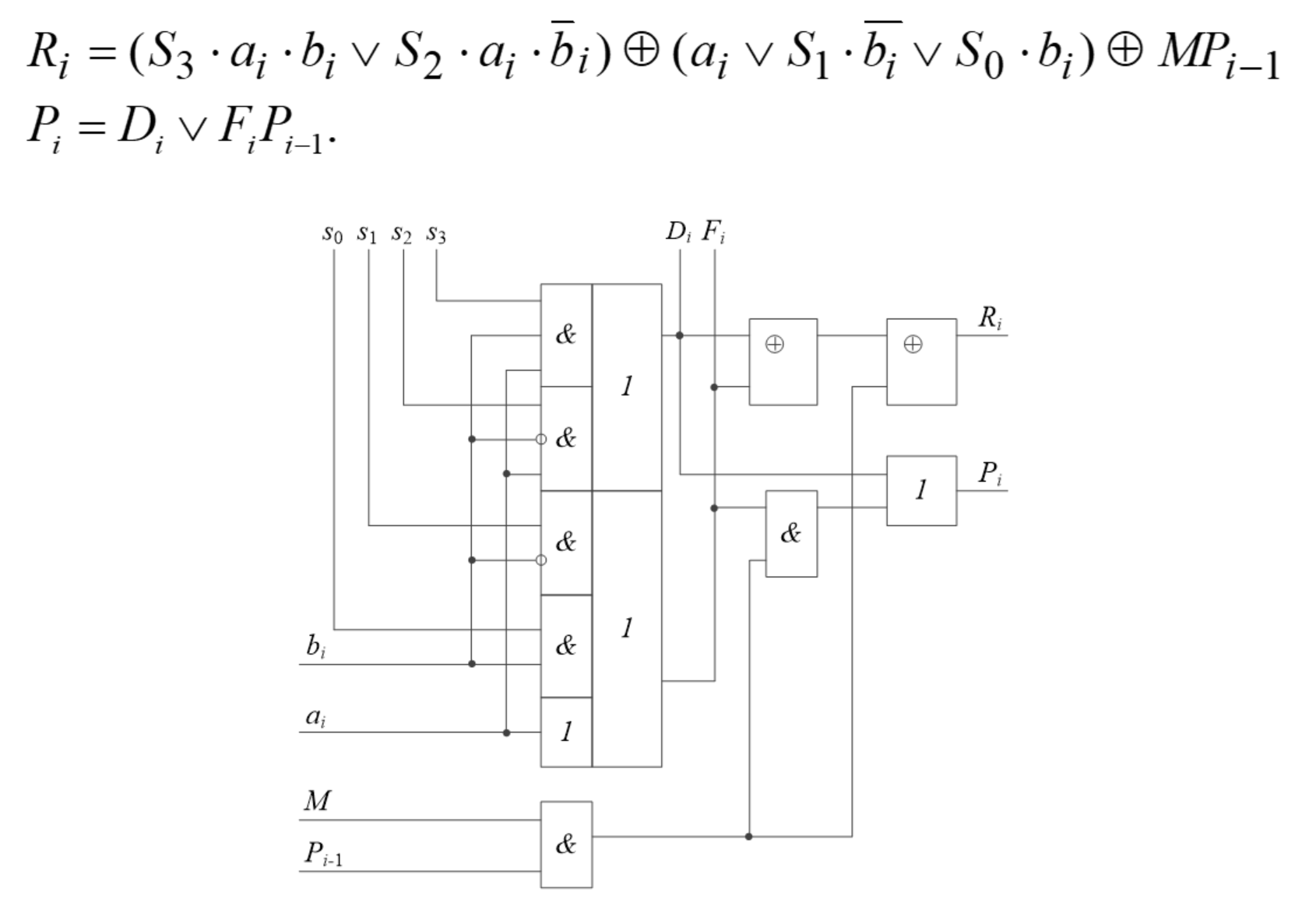

Другой подход к построению АЛУ предполагает вывод оптимальных выражений, в которых конкретные значения управляющих сигналов преобразуют выражение так, чтобы оно выполняло требуемую операцию. В рассмотренном примере поддерживается 48 операций (но некоторые повторяются):

- 32 арифметических:

- 16 операций когда M=1, Pi-1=0;

- 16 операций когда M=1, Pi-1=1;

- 16 логических, когда M=0 (от Pi-1 ничего не зависит).

S — управляющее слово, a, b — операнды, P — перенос, M — выключатель переноса, R - результат операции. Индексы внизу указывают на то, что выражение относится к отдельному i-ому биту результата.

Например, чтобы выполнить операцию A ИЛИ B, надо подать управляющие сигналы S = 0001, M = 0, тогда в выражении R сократятся импликанты с S3, S2, S1 и M, потому что они равны нулю, и останется только R = a | b. Разработка, отладка и изменение конфигурации таких АЛУ сложнее, чем при первом подходе, однако можно получить гораздо больше (пусть и не часто используемых) операций, при меньшем критическом пути.

В конце лекции посмотрели на организацию блоков сравнения, логических и арифметических сдвигов.

Основные материалы лекции

- Ссылка на видеозапись лекции

- Как и всегда в этом источнике, отличное доступное описание работы и принципов построения сумматоров, в том числе с ускоренным и префиксным переносом, компараторов, АЛУ и схем сдвига [Харрис и Харрис. Цифровая схемотехника и архитектура компьютера — параграфы 5.2.1 — 5.2.5]

- Про вариант синтезируемого через выражения АЛУ читай тут [Кафедра ВТ. Микропроцессорные средства и системы — Лекция 1.2]

Дополнительные материалы к лекции для саморазвития

- Еще один вариант АЛУ, с коротким описанием на страничку, можно посмотреть тут [Таненбаум и Остин. Архитектура компьютера — Глава 3., Основные логические схемы, Арифметические схемы, подраздел Арифметико-логические устройства]

Популярные материалы

- Если есть хоть малейшая толика непонимания как все происходит внутри сумматора и как это все может быть физически реализовано, то крайне рекомендую посмотреть это 14-минутное видео, в котором очень доступно все рассказано