mirror of

https://github.com/MPSU/APS.git

synced 2026-04-25 05:35:33 +00:00

Для повышения читаемости, приоритетный мультиплексор разбит на каскад двухвходовых мультиплексоров.

Лабораторная работа 11 "Интеграция подсистемы прерываний"

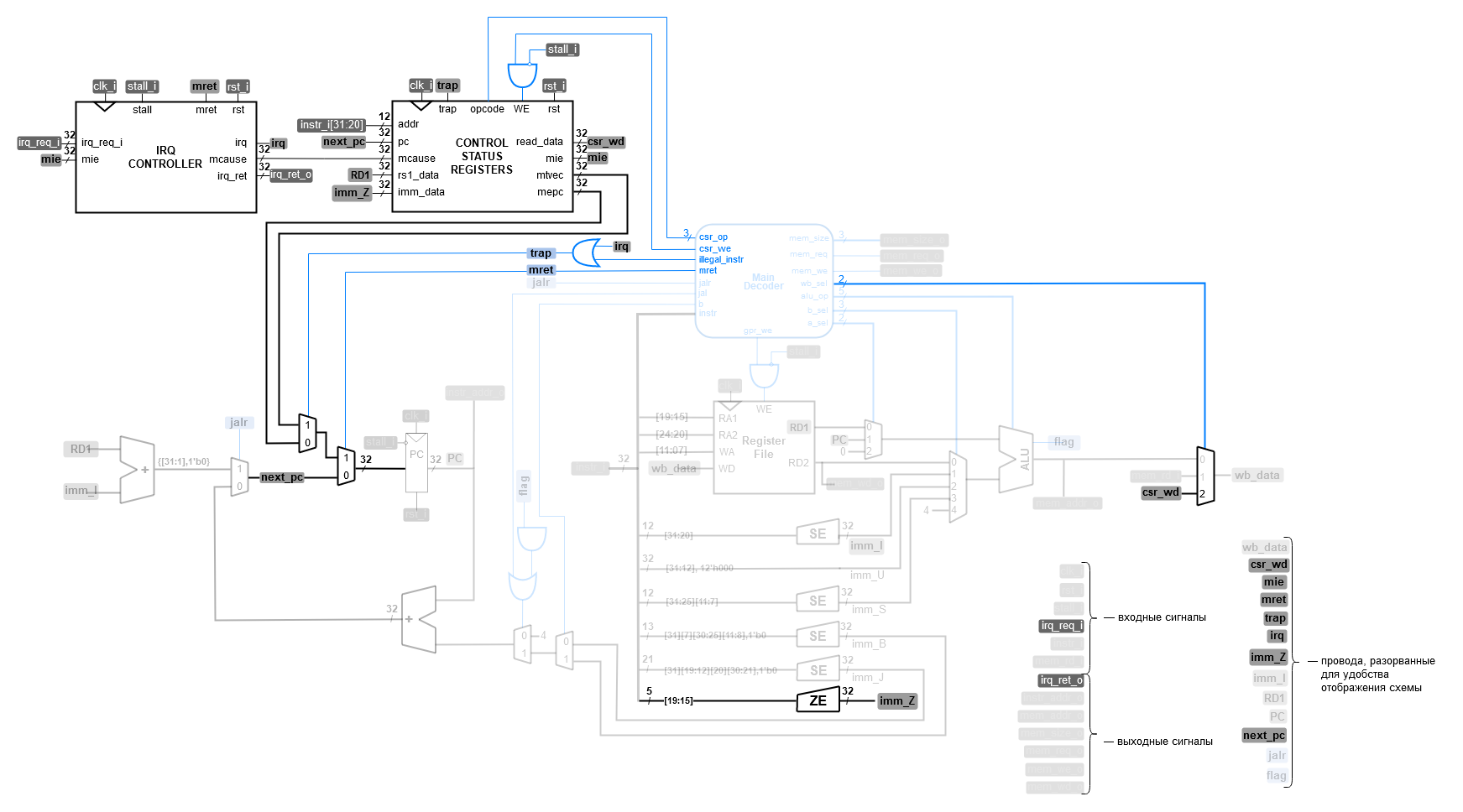

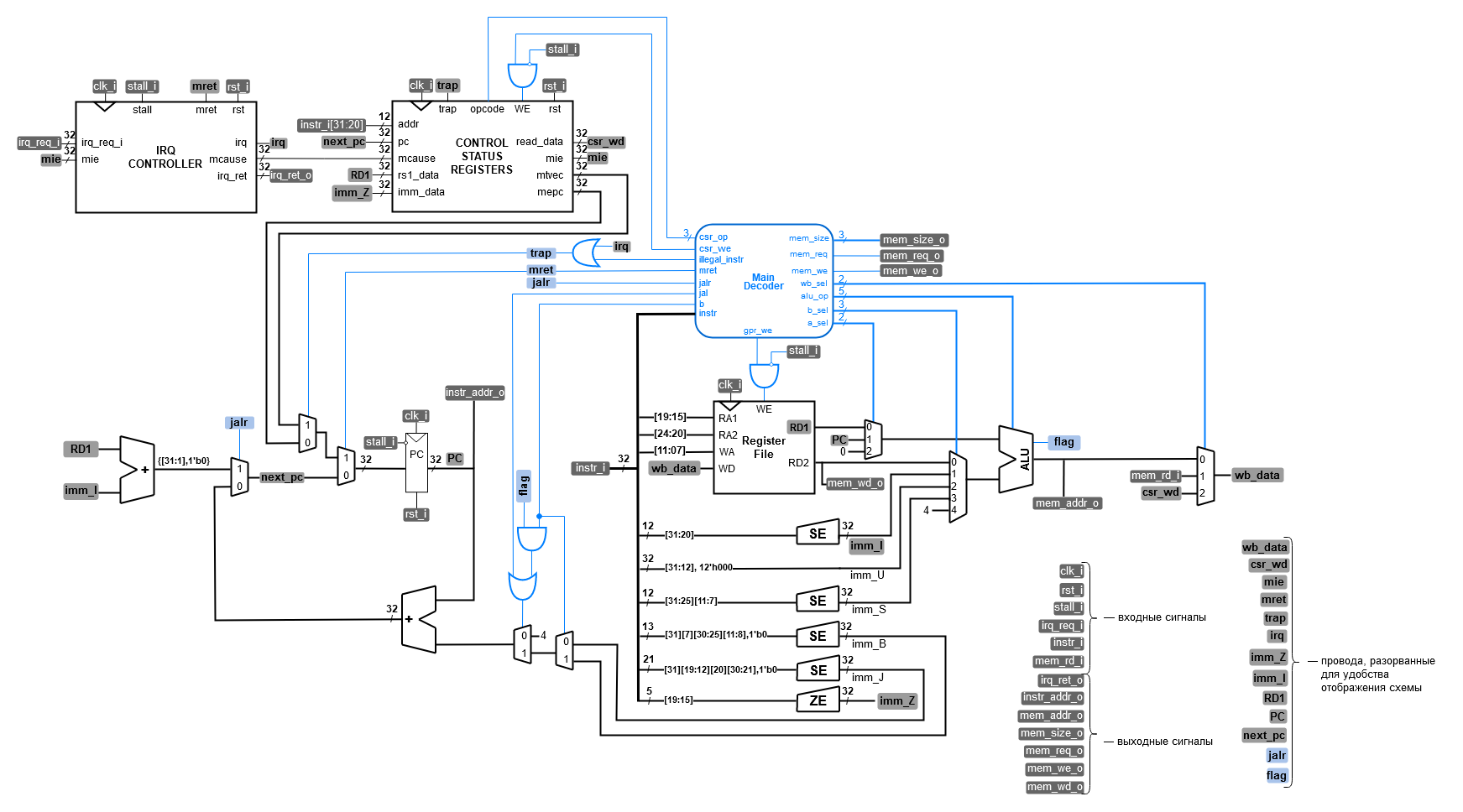

После реализации подсистемы прерываний, её необходимо интегрировать в процессорную систему. Для этого необходимо обновить модуль riscv_core по приведенной ниже схеме:

Задание

Интегрировать модули csr_controller и irq_controller в модуль riscv_core.

Порядок выполнения работы

- Интегрируйте модули

csr_controllerиirq_controllerв модульriscv_core.- Обратите внимание, что что в модуле

riscv_coreпоявились новые входные и выходные сигналы:irq_req_iиirq_ret_o. Эти сигналы должны быть использованы при подключенииriscv_coreв модулеriscv_unit.- На вход

irq_req_iпока что необходимо подать32'd0(в следующей лабораторной это будет изменено). - При подключении сигнала

irq_ret_oможно ничего не указывать (до следующей лабораторной к нему ничего не будет подключено).

- На вход

- Обратите внимание, что что в модуле

- После интеграции модулей, проверьте процессорную систему с помощью программы из ЛР10 с помощью предоставленного тестбенча.