Курс лабораторных работ

Содержание

- Курс лабораторных работ

- Содержание

- Полезное

- Порядок выполнения лабораторных работ для групп

- Обзор лабораторных работ

- 1. Сумматор. Verilog HDL (Adder)

- 2. Арифметико-логическое устройство (ALU)

- 3. Регистровый файл и память (RF)

- 4. Простейшее программируемое устройство (PPD)

- 5. Основной дешифратор команд (MD)

- 6. Тракт данных (DP)

- 7. Внешняя память

- 8. Блог загрузки и сохранения данных (LSU)

- 9 Интеграция LSU

- 10. Подсистема прерывания (IC)

- 11. Интеграция подсистемы прерывания

- 12. Периферийные устройства (PU)

- 13. Программирование на языке высокого уровня

Полезное

- Студенческий сервер

- Создание базового проекта с прошивкой ПЛИС в Vivado

- Базовые конструкции Verilog

- Список типичных ошибок в Vivado и SystemVerilog

- Тестовое окружение

- Готовые модули

Порядок выполнения лабораторных работ для групп

ИБ, ИКТ, КТ, РТ

- Сумматор (01. Adder)

- АЛУ (02. Arithmetic-logic unit)

- Регистровый файл и внешняя память (03. Register file and memory)

- Простейшее программируемое устройство (04. Primitive programmable device)

ПИН, ПМ

- Сумматор (01. Adder)

- АЛУ (02. Arithmetic-logic unit)

- Регистровый файл и внешняя память (03. Register file and memory)

- Простейшее программируемое устройство (04. Primitive programmable device)

- Основной дешифратор (05. Main decoder)

-

- Тракт данных (06. Datapath)

- Интеграция блока загрузки и сохранения (09. LSU Integration)

- Интеграция подсистемы прерываний (11. Interrupt Integration)

- Периферийные устройства (12. Peripheral units)

- Программирование (13. Programming)

ИВТ

- АЛУ (02. Arithmetic-logic unit)

-

- Память (03. Register file and memory),

- Простейшее программируемое устройство (04. Primitive programmable device)

- Основной дешифратор (05. Main decoder)

- Тракт данных (06. Datapath)

-

- Модуль загрузки и сохранения (08. Load-store unit)

- Интеграция блока загрузки и сохранения (09. LSU Integration)

-

- Контроллер прерываний (10. Interrupt subsystem)

- Интеграция подсистемы прерываний (11. Interrupt Integration)

- Периферийные устройства (12. Peripheral units)

- Программирование (13. Programming)

Обзор лабораторных работ

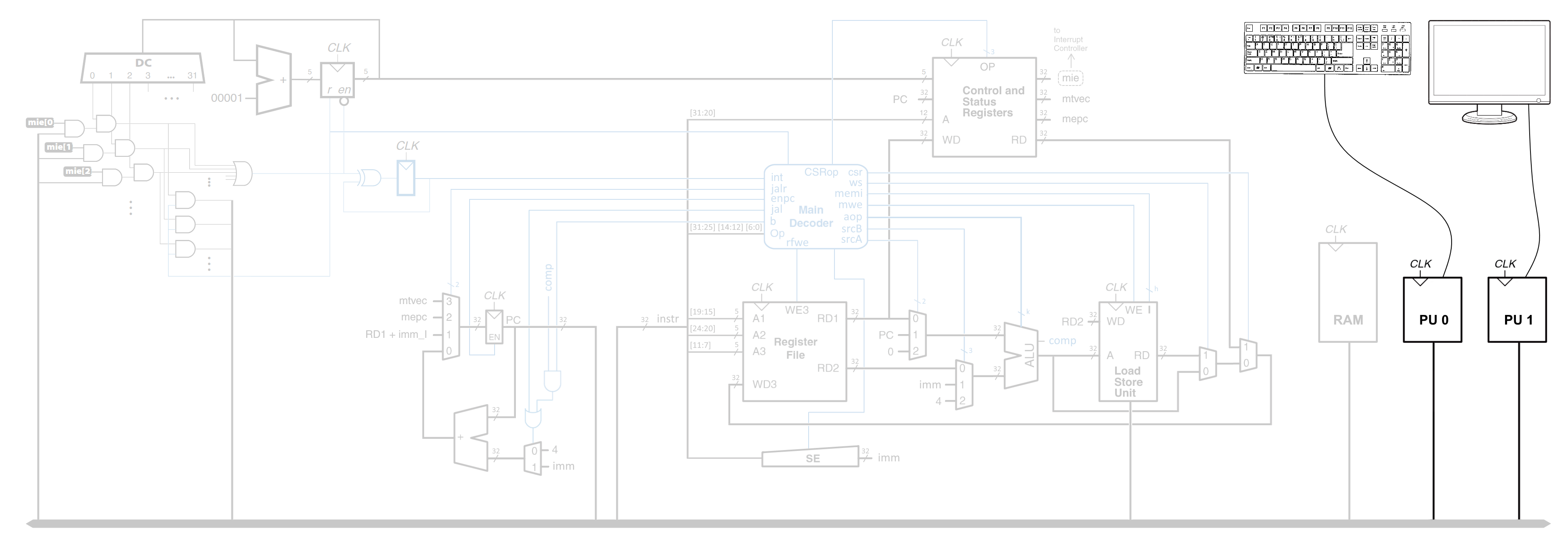

Курс Архитектур процессорных систем включает в себя цикл из 13 лабораторных работ (10 основных + 3 вспомогательных), в течение которых используя язык описания аппаратуры Verilog HDL на основе FPGA (ПЛИС, программируемая логическая интегральная схема), с нуля, последовательно, создается система, под управлением процессора с архитектурой RISC-V, управляющего периферийными устройствами и программируемого на языке высокого уровня C++.

Создаваемая система на ПЛИС состоит из: процессора, памяти, контроллера прерываний и контроллеров периферийных устройств.

Выполнение лабораторных работ это последовательный процесс в результате которого будет освоен ряд различных инструментов и средств. В общих словах это:

Verilog HDL - язык описания аппаратуры, благодаря которому схемы не рисуются, а описываются с помощью текста (кода).

Testbench - тестовые окружения, которые представляют собой несинтезируемые (то есть не существующие в реальном физическом мире) блоки, созданные на языке Verilog HDL для автоматического тестирования разрабатываемых устройств и проверки их корректной работоспособности.

FPGA - программируемая логическая интегральная схема (ПЛИС), изменяя внутреннюю конфигурацию которой можно создать любые цифровые устройства (в рамках предоставляемых ресурсов).

Vivado - система автоматизированного проектирования, которая превращает Verilog-код в конфигурацию и прошивает ей ПЛИС на отладочной плате.

Архитектура RISC-V - открытая и свободная система команд и процессорная архитектура на основе концепции RISC для микропроцессоров и микроконтроллеров.

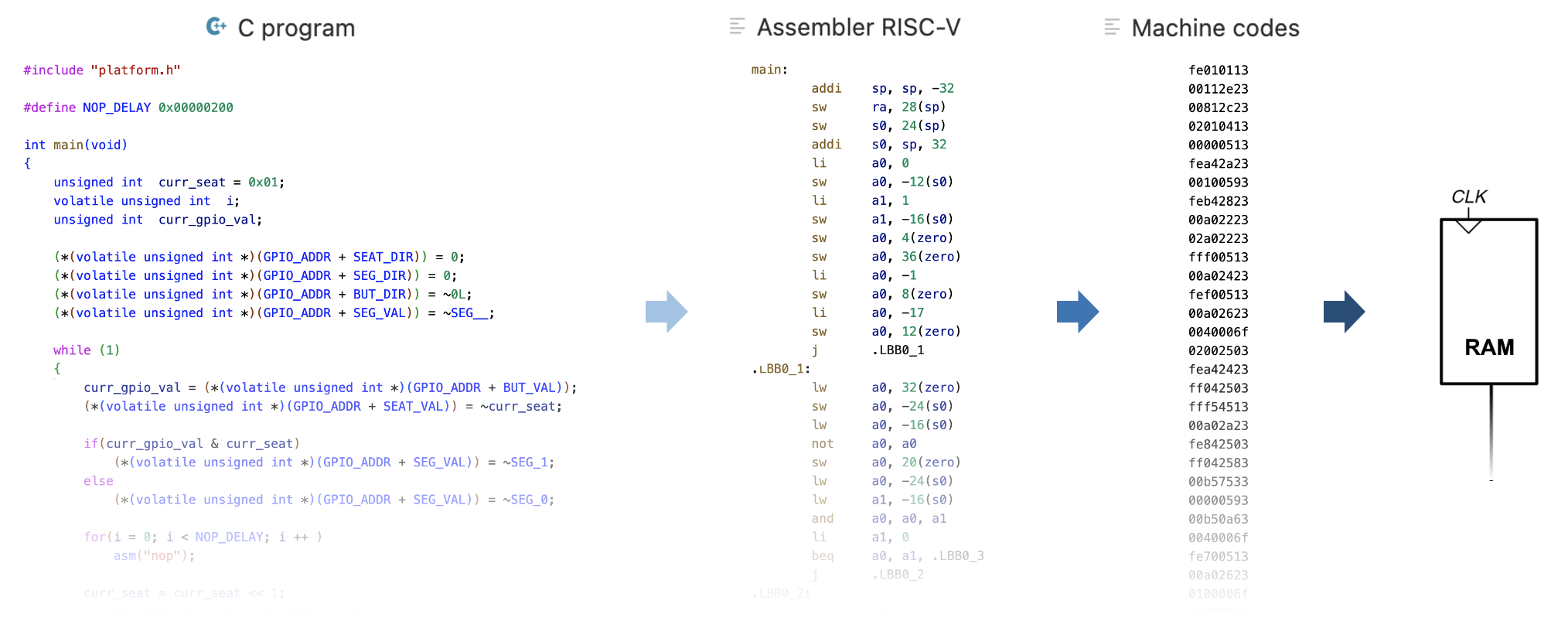

Язык ассемблера RISC-V - список основных команд и особенности их использования и написания программ.

Ассемблер RISC-V - программа, которая превращает код, написанный на языке ассемблера RISC-V в машинные инструкции для процессора с архитектурой RISC-V.

Далее приводится краткое описание и цель каждой отдельной лабораторной работы.

1. Сумматор. Verilog HDL (Adder)

На первой лабораторной работе изучаются базовые конструкции языка описания аппаратуры Verilog HDL, с помощью которого разрабатывается цифровой сумматор из примитивных логических вентилей, который, в последствии, конфигурируется в ПЛИС и его работа проверяется на отладочном стенде.

На первой лабораторной работе изучаются базовые конструкции языка описания аппаратуры Verilog HDL, с помощью которого разрабатывается цифровой сумматор из примитивных логических вентилей, который, в последствии, конфигурируется в ПЛИС и его работа проверяется на отладочном стенде.

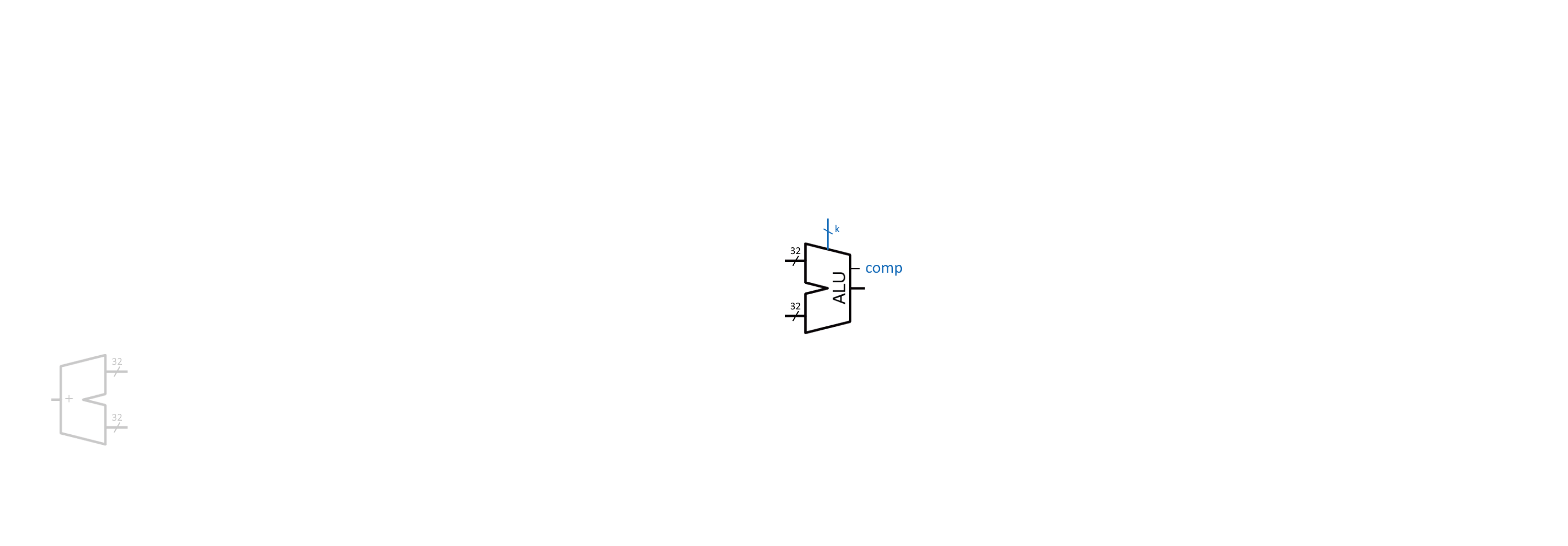

2. Арифметико-логическое устройство (ALU)

На второй лабораторной изучаются новые конструкции языка Verilog HDL, на основе которых разрабатывается блок арифметико-логического устройства (АЛУ). АЛУ - это устройство, на входы которого подаются операнды, над которыми нужно выполнить некоторую операцию (сложение, вычитание и тому подобное) и код операции, которую нужно выполнить, а на выходе появляется результат этой операции. Проще говоря АЛУ - это "калькулятор" процессора.

На второй лабораторной изучаются новые конструкции языка Verilog HDL, на основе которых разрабатывается блок арифметико-логического устройства (АЛУ). АЛУ - это устройство, на входы которого подаются операнды, над которыми нужно выполнить некоторую операцию (сложение, вычитание и тому подобное) и код операции, которую нужно выполнить, а на выходе появляется результат этой операции. Проще говоря АЛУ - это "калькулятор" процессора.

Для проверки правильной работоспособности АЛУ в конце лабораторной работы, на языке Verilog HDL, пишется testbench (тестовое окружение), которое автоматически проверяет корректность его реализации.

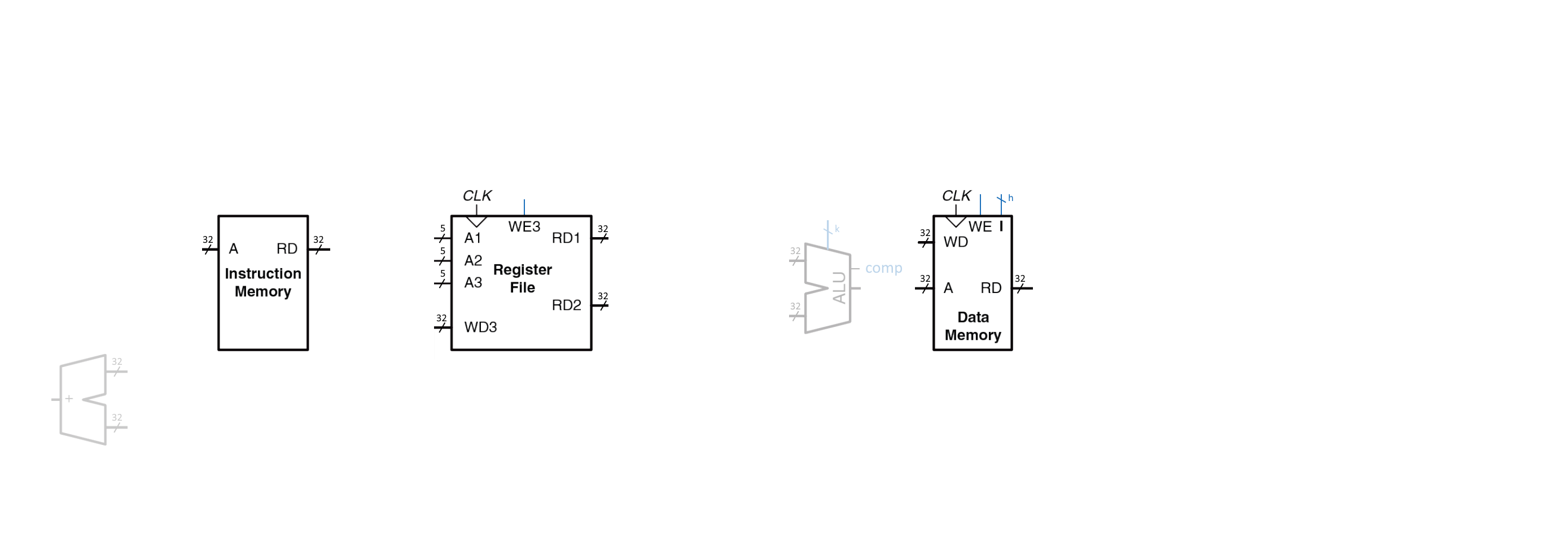

3. Регистровый файл и память (RF)

На третьей лабораторной разрабатываются элементы памяти для будущего процессора: память команд, память данных и регистровый файл. В памяти команд будет храниться программа, которую будет выполнять процессор. В памяти данных хранятся данные, которые будут обрабатываться процессором. Регистровый файл - это маленькая память, тоже с данными, которые могут быть поданы непосредственно на АЛУ. Особенность RISC-архитектур в том, что данные перед обработкой необходимо перенести из памяти данных в регистровый файл, только после этого к ним можно применять различные операции.

На третьей лабораторной разрабатываются элементы памяти для будущего процессора: память команд, память данных и регистровый файл. В памяти команд будет храниться программа, которую будет выполнять процессор. В памяти данных хранятся данные, которые будут обрабатываться процессором. Регистровый файл - это маленькая память, тоже с данными, которые могут быть поданы непосредственно на АЛУ. Особенность RISC-архитектур в том, что данные перед обработкой необходимо перенести из памяти данных в регистровый файл, только после этого к ним можно применять различные операции.

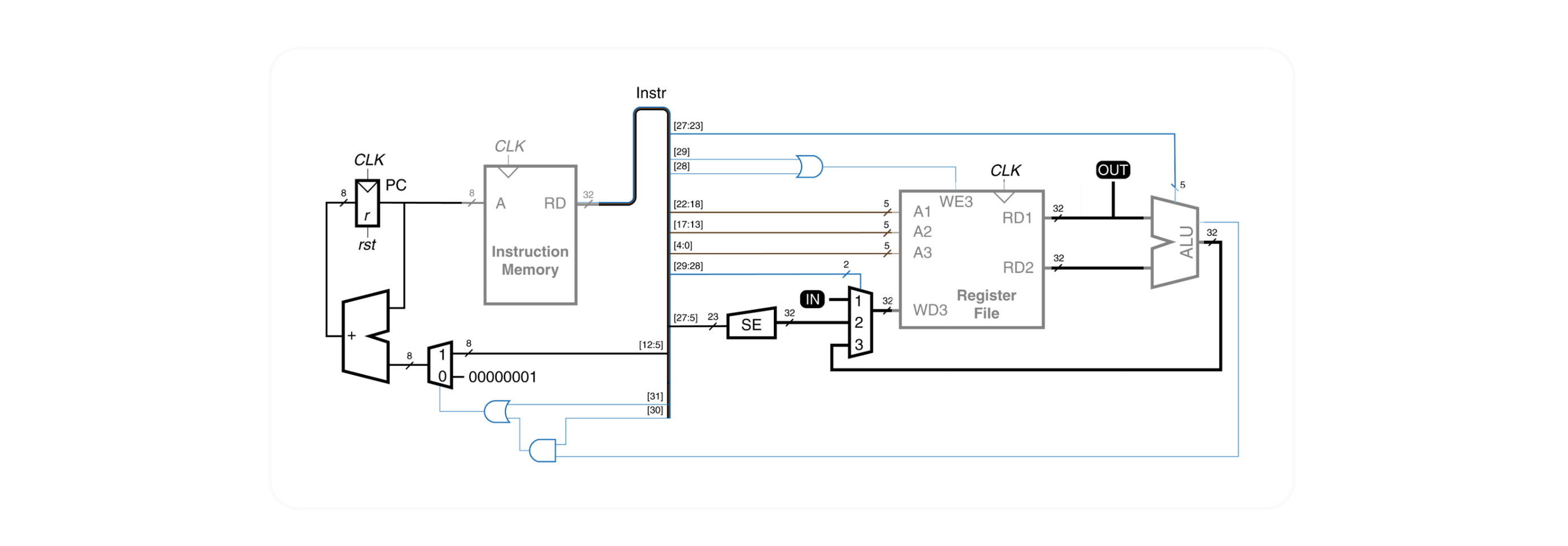

4. Простейшее программируемое устройство (PPD)

Эта работа – небольшое отступление от реализации процессора с архитектурой RISC-V и нужна для более глубокого понимания принципов работы и организации программируемых устройств. В рамках четвертой лабораторной работы из реализованных блоков собирается примитивное программируемое устройство, для которого пишется программа в машинных кодах.

Эта работа – небольшое отступление от реализации процессора с архитектурой RISC-V и нужна для более глубокого понимания принципов работы и организации программируемых устройств. В рамках четвертой лабораторной работы из реализованных блоков собирается примитивное программируемое устройство, для которого пишется программа в машинных кодах.

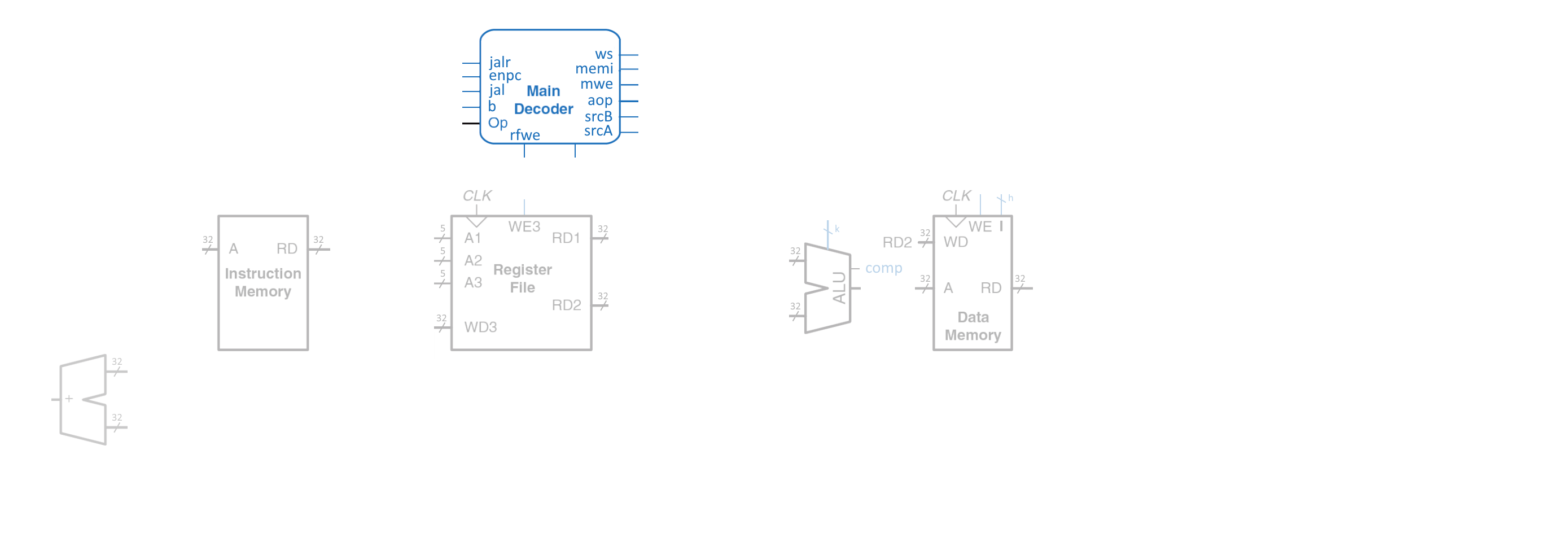

5. Основной дешифратор команд (MD)

Пятая лабораторная посвящена разработке устройства управления – основному дешифратору команд. Функция основного дешифратора - получать на вход коды выполняемых операций и преобразовывать их в управляющие сигналы для всех блоков процессора (АЛУ, память, регистровый файл, мультиплексоры). Работа требует внимательности в реализации, а ее результат проверяется заранее подготовленными автоматическими тестами.

Пятая лабораторная посвящена разработке устройства управления – основному дешифратору команд. Функция основного дешифратора - получать на вход коды выполняемых операций и преобразовывать их в управляющие сигналы для всех блоков процессора (АЛУ, память, регистровый файл, мультиплексоры). Работа требует внимательности в реализации, а ее результат проверяется заранее подготовленными автоматическими тестами.

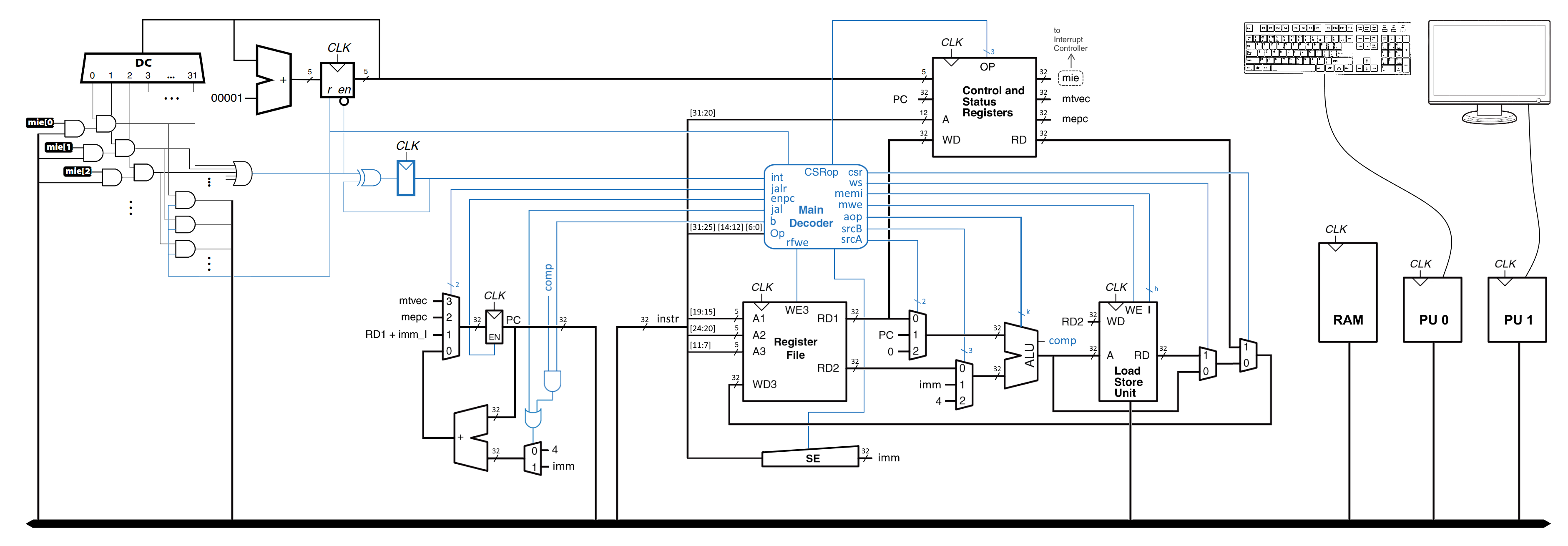

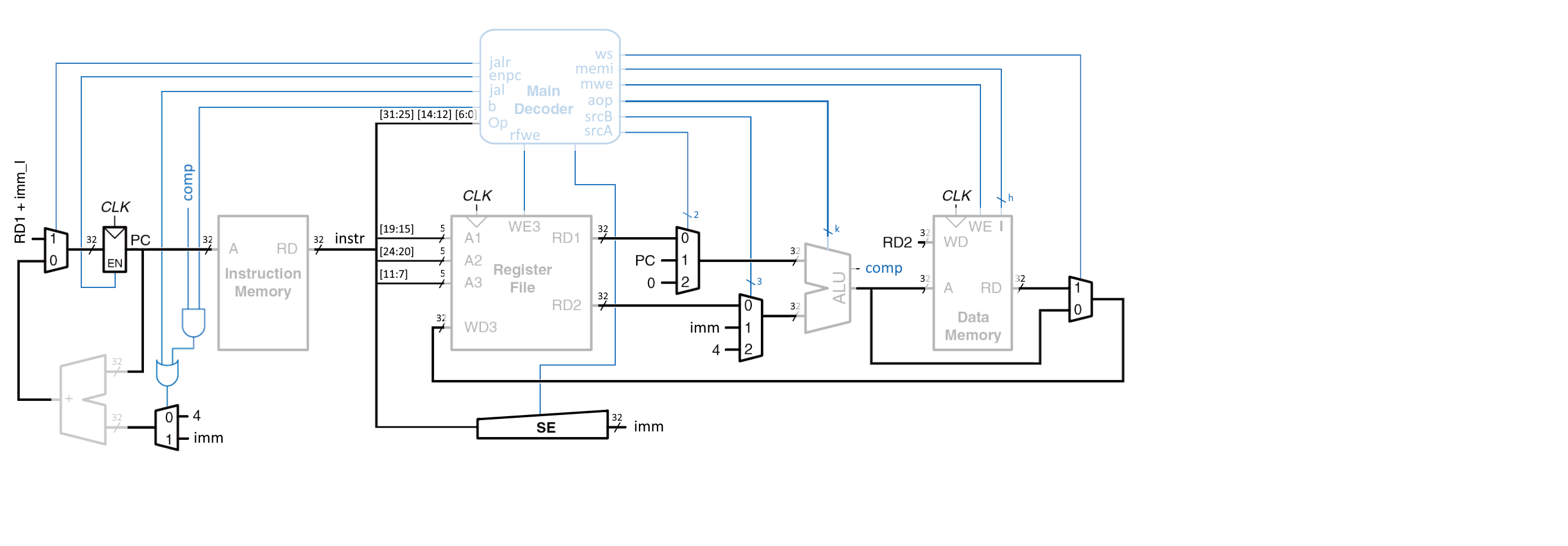

6. Тракт данных (DP)

Разработанные блоки объединяются, образуя тракт данных, управляемый основным дешифратором команд. Результатом шестой лабораторной работы является однотактный процессор, с архитектурой RISC-V, поддерживающий стандартный набор целочисленных инструкций RV32I. В качестве проверки на процессоре запускаются программы, заранее написанные на языке ассемблера RISC-V. Сравнивается результат полученный на симуляторе и на разработанном процессоре.

Разработанные блоки объединяются, образуя тракт данных, управляемый основным дешифратором команд. Результатом шестой лабораторной работы является однотактный процессор, с архитектурой RISC-V, поддерживающий стандартный набор целочисленных инструкций RV32I. В качестве проверки на процессоре запускаются программы, заранее написанные на языке ассемблера RISC-V. Сравнивается результат полученный на симуляторе и на разработанном процессоре.

7. Внешняя память

Недостатком реализации процессора из предыдущей лабораторной работы была его неспособность выполнять операции LB, LBU, SB, LH, LHU, SH. Отчасти это связано с ограничением реализованной ранее памяти (в этой памяти не было возможности обновить отдельный байт в ячейке памяти).

Данная вспомогательная лабораторная работа позволяет реализовать память без этого ограничения.

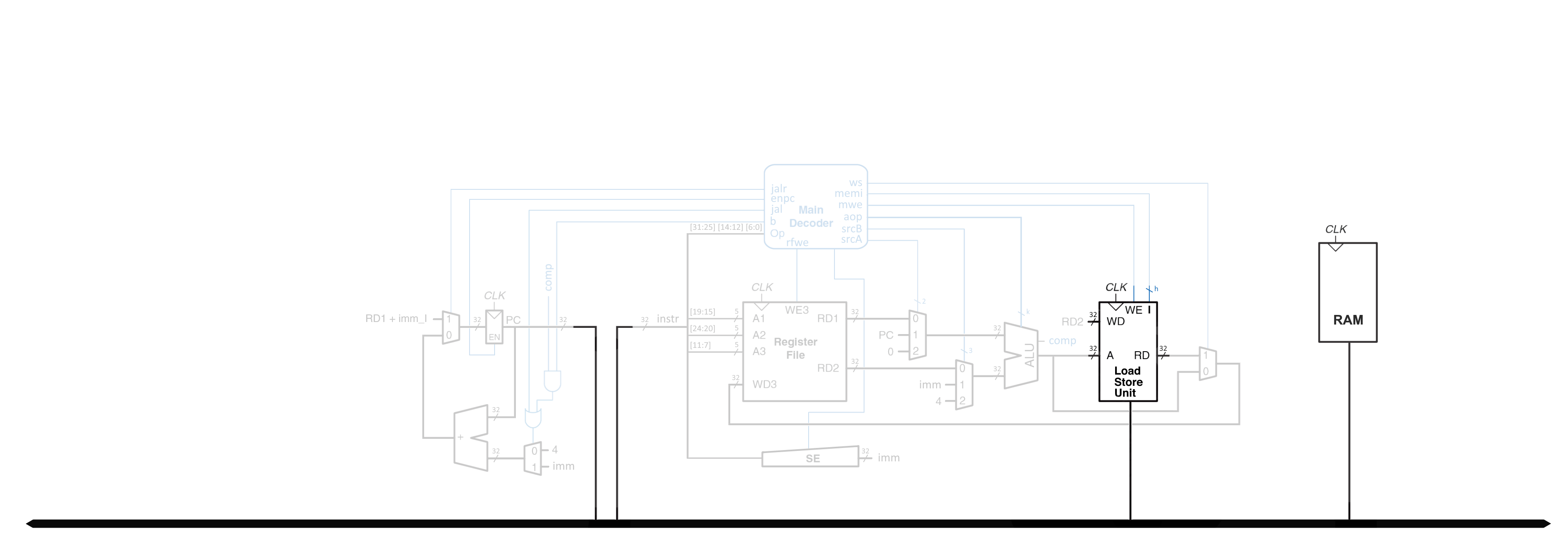

8. Блог загрузки и сохранения данных (LSU)

Для корректного исполнения инструкций LB, LBU, SB, LH, LHU, SH мало использовать память с побайтовой записью. Необходимо также уметь управлять этой памятью, определенным образом подготавливать данные как для записи в память данный, так и для записи в регистровый файл, а также следить за тем, чтобы за время работы с памятью, программа процессора не начала исполняться дальше. Все эти задачи возлагаются на специальный модуль, который называется Блок загрузки и сохранения (Load and Store Unit, LSU)

9 Интеграция LSU

Вспомогательная лабораторная работа по интеграции реализованного ранее блока загрузки и сохранения, а также новой памяти данных в модуль riscv_unit.

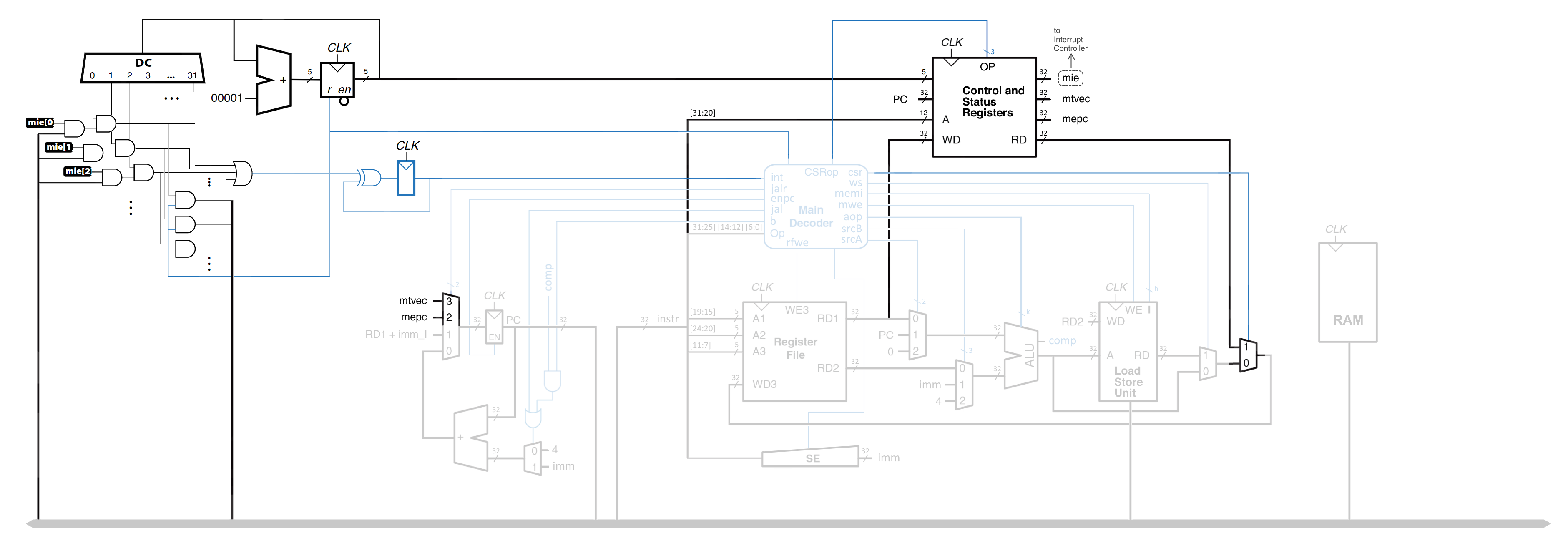

10. Подсистема прерывания (IC)

Одной из основных функций процессоров является возможность реагировать на внешние события (дернуть мышку, нажать кнопку и т.п.), автоматически запуская, при их возникновении, соответствующие программы. В данной лабораторной создается и подсистема прерывания, к которой относятся контроллер прерываний с циклическим опросом и блок регистров статуса и управления.

11. Интеграция подсистемы прерывания

Вспомогательная лабораторная работа по интеграции реализованной ранее подсистемы прерывания.

12. Периферийные устройства (PU)

В данной лабораторной создаются и подключаются к общей шине и подсистеме прерывания контроллеры периферийных устройств: переключатели, светодиоды, клавиатура, семисегментные дисплеи а так же контроллер uart.

13. Программирование на языке высокого уровня

В рамках данной лабораторной настраивается компилятор GCC для RISC-V и для разработанной системы пишется программное обеспечение на языке программирования C++.