mirror of

https://github.com/MPSU/APS.git

synced 2026-04-27 22:55:33 +00:00

Раньше в вивадо была проблема с использованием mem-файлов. Они нормально моделировались, но при этом не использовались в синтезе, пока им не выставишь тип "Memory Initialization File". Однако с выставлением этого типа файл нельзя было открыть в вивадо (и даже поменять тип этого файла). Поэтому, все файлы в курсе носили расширение .txt, чтобы их можно было легко открыть в любом другом редакторе, а в вивадо выставлялся злополучный тип "Memory Initialization File" вручную. Сейчас же, судя по всему, вивадо нормально выполняет синтез и с "Memory File" тоже, а значит нет нужды в каком-либо изменении типов, лишь бы файлы носили расширение .mem. При этом файлы этого типа можно открывать и редактировать в редакторе вивадо.

Лабораторная работа 11 "Интеграция подсистемы прерываний"

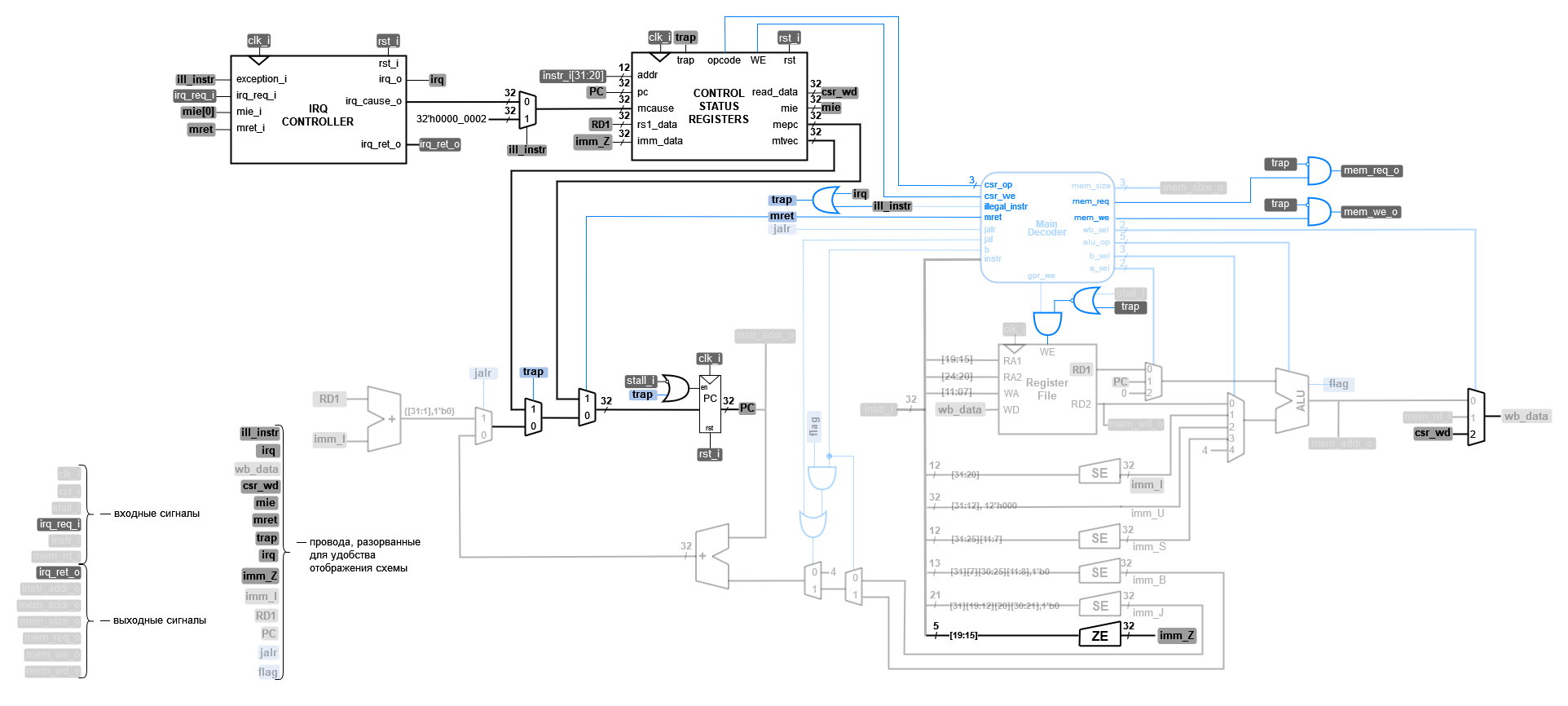

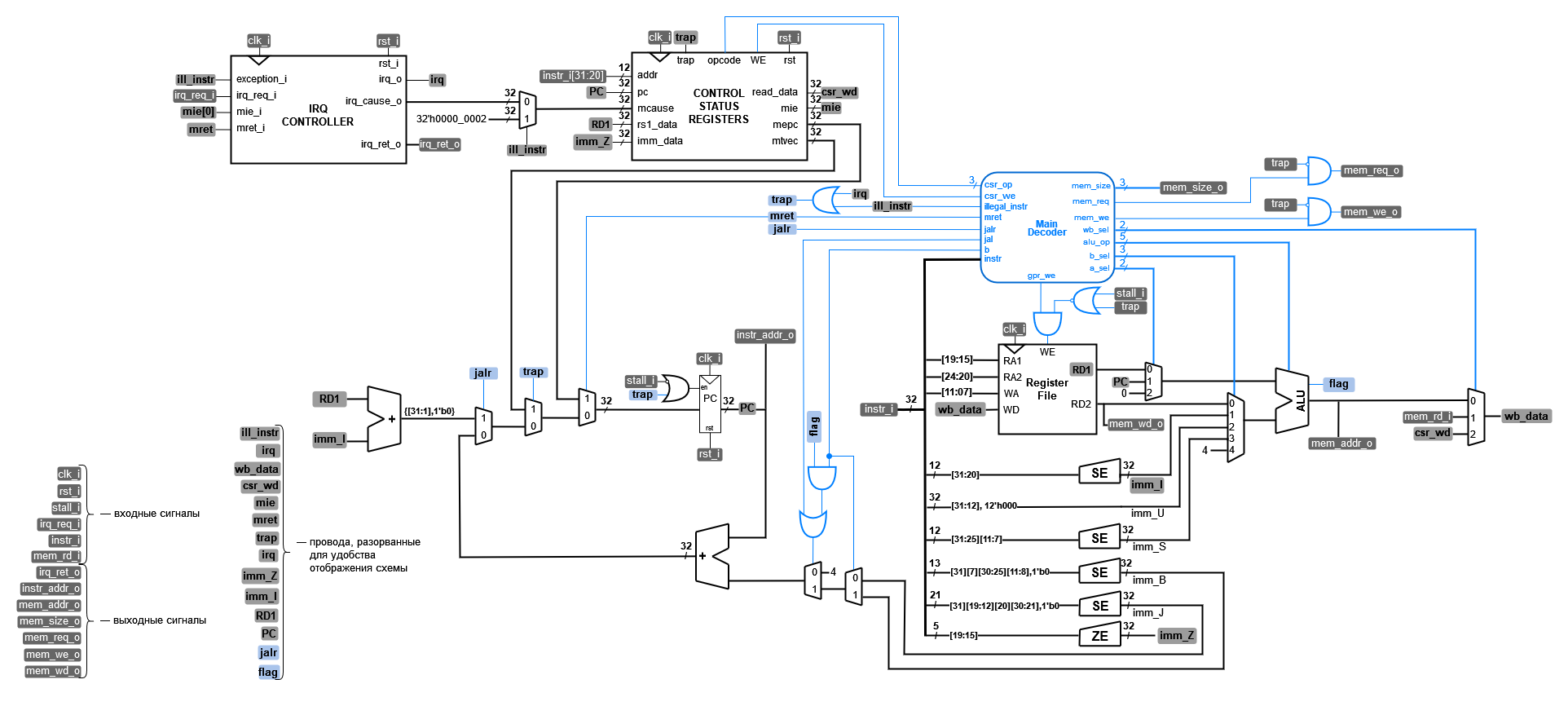

После реализации подсистемы прерываний, её необходимо интегрировать в процессорную систему. Для этого необходимо обновить модуль riscv_core по приведенной ниже схеме:

Задание

Интегрировать модули csr_controller и irq_controller в модуль riscv_core.

Порядок выполнения работы

- Интегрируйте модули

csr_controllerиirq_controllerв модульriscv_core.- Обратите внимание, что что в модуле

riscv_coreпоявились новые входные и выходные сигналы:irq_req_iиirq_ret_o. Эти сигналы должны быть использованы при подключенииriscv_coreв модулеriscv_unit.- Ко входу

irq_req_iдолжен быть подключен проводirq_req, другой конец которого пока не будет ни к чему подключен (в следующей лабораторной это будет изменено). - К выходу

irq_ret_oнеобходимо подключить проводirq_ret, который также пока не будет использован.

- Ко входу

- Обратите внимание, что что в модуле

- После интеграции модулей, проверьте процессорную систему с помощью программы, текст которой был представлен в ЛР10 с помощью предоставленного тестбенча.